# 4-Channel, 104 MSPS Digital Transmit Signal Processor (TSP)

# AD6623

#### **FEATURES**

Pin Compatible to the AD6622

18-Bit Parallel Digital IF Output Real or Interleaved Complex

18-Bit Bidirectional Parallel Digital IF Input/Output

Allows Cascade of Chips for Additional Channels

Clipped or Wrapped Over Range

Two's Complement or Offset Binary Output

Four Independent Digital Transmitters in Single Package RAM Coefficient Filter (RCF)

Programmable IF and Modulation for Each Channel Programmable Interpolating RAM Coefficient Filter  $\pi/4$ -DQPSK Differential Phase Encoder

3π/8-PSK Linear Encoder

8-PSK Linear Encoder

Programmable GMSK Look-Up Table

Programmable QPSK Look-Up Table

All-Pass Phase Equalizer

**Programmable Fine Scaler**

**Programmable Power Ramp Unit**

**High Speed CIC Interpolating Filter**

Digital Resampling for Noninteger Interpolation Rates NCO Frequency Translation

Carrier Output from DC to 52 MHz

Spurious Performance Better than -100 dBc

Separate 3-Wire Serial Data Input for Each Channel Bidirectional Serial Clocks and Frames

Microprocessor Control

2.5 V CMOS Core, 3.3 V Outputs, 5 V Inputs

JTAG Boundary Scan

#### **APPLICATIONS**

Cellular/PCS Base Stations

Micro/Pico Cell Base Stations

Wireless Local Loop Base Stations

Multicarrier, Multimode Digital Transmit

GSM EDGE 15136 PHS 1595 TDS CDMA LIMTS

GSM, EDGE, IS136, PHS, IS95, TDS CDMA, UMTS, CDMA2000

Phased Array Beam Forming Antennas

**Software Defined Radio**

Tuning Resolution Better than 0.025 Hz

**Real or Complex Outputs**

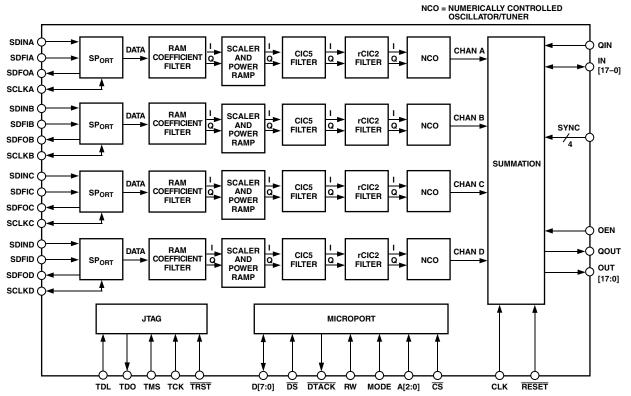

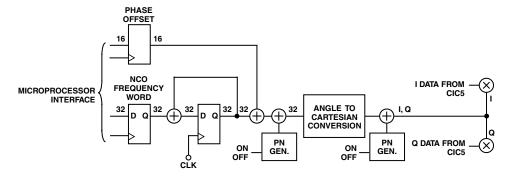

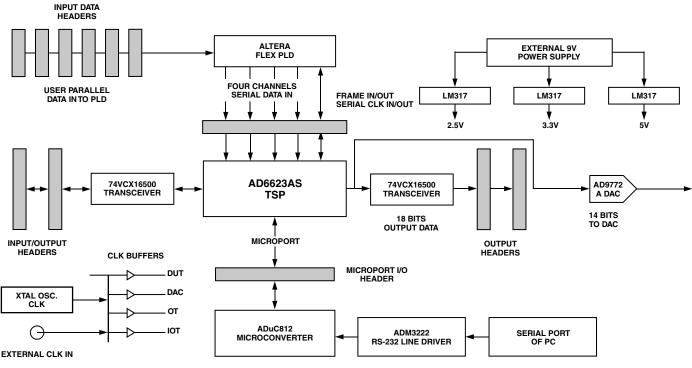

#### FUNCTIONAL BLOCK DIAGRAM

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

# AD6623\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖳

View a parametric search of comparable parts.

## **DOCUMENTATION**

#### **Application Notes**

- AN-835: Understanding High Speed ADC Testing and Evaluation

- AN-851: A WiMax Double Downconversion IF Sampling Receiver Design

#### **Data Sheet**

AD6623: 4-Channel, 104 MSPS Digital Transmit Signal Processor (TSP) Data Sheet

#### **Product Highlight**

Introducing Digital Up/Down Converters: VersaCOMM™ Reconfigurable Digital Converters

### **TOOLS AND SIMULATIONS**

AD6623 IBIS Models

# REFERENCE MATERIALS 🖵

#### **Technical Articles**

- Basics of Designing a Digital Radio Receiver (Radio 101)

- Digital Up/Down Converters: VersaCOMM™ White Paper

- · Smart Partitioning Eyes 3G Basestation

# **DESIGN RESOURCES**

- ad6623 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS 🖳

View all ad6623 EngineerZone Discussions.

### SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

# **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

### TABLE OF CONTENTS

| FEATURES 1<br>APPLICATIONS 1                      | Start with SoftSync                                                                                       |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| FUNCTIONAL BLOCK DIAGRAM                          | Hop30                                                                                                     |

| PRODUCT DESCRIPTION                               | Set Frequency No Hop                                                                                      |

| FUNCTIONAL OVERVIEW                               | Hop with SoftSync                                                                                         |

| RECOMMENDED OPERATING CONDITIONS 4                | Hop with Pin Sync                                                                                         |

| ELECTRICAL CHARACTERISTICS                        | Beam         3           Set Phase No Beam         3                                                      |

| LOGIC OUTPUTS                                     | Beam with SoftSync                                                                                        |

| IDD SUPPLY CURRENT                                | Beam with Pin Sync                                                                                        |

| POWER DISSIPATION 4                               | Time Slot (Ramp)                                                                                          |

| GENERAL TIMING CHARACTERISTICS                    | Set Output Power, No Ramp                                                                                 |

| MICROPROCESSOR PORT TIMING CHARACTERISTICS 6      | Time Slot (Ramp) with SoftSync                                                                            |

| MICROPROCESSOR PORT, MODE INM (MODE = $0$ ) 6     | Time Slot with Pin Sync                                                                                   |

| MICROPROCESSOR PORT, MOTOROLA (MODE = 1)          | JTAG INTERFACE                                                                                            |

| TIMING DIAGRAMS                                   | SCALING                                                                                                   |

| ABSOLUTE MAXIMUM RATINGS                          | Multicarrier Scaling                                                                                      |

| EXPLANATION OF TEST LEVELS 10                     | MICROPORT INTERFACE 34                                                                                    |

| ORDERING GUIDE                                    | Microport Control                                                                                         |

| PIN CONFIGURATION – 128-Lead MQFP                 | EXTERNAL MEMORY MAP                                                                                       |

| 128-PIN FUNCTION DESCRIPTION                      | Intel Nonmultiplexed Mode (INM)                                                                           |

| PIN CONFIGURATION – 196-Lead CSPBGA               | Motorola Nonmultiplexed Mode (MNM)                                                                        |

| 196-PIN FUNCTION DESCRIPTION                      | External Address 7 Upper Address Register (UAR)                                                           |

| POWER SUPPLY                                      | External Address 6 Lower Address Register (LAR)                                                           |

| INPUTS                                            | External Address 5 SoftSync                                                                               |

| CONTROL                                           | External Address 4 Sleep                                                                                  |

| OUTPUTS                                           | INTERNAL CONTROL REGISTERS AND ON-CHIP RAM                                                                |

| JTAG AND BIST                                     | AD6623 and AD6622 Compatibility                                                                           |

| CONTROL REGISTER ADDRESS NOTATION                 | Common Function Registers (not associated with a particular channel) 30                                   |

| SERIAL DATA PORT                                  | Channel Function Registers (0x1xx = Ch. A,                                                                |

| Serial Master Mode (SCS = 0)                      | 0x2xx = Ch. B, 0x3xx = Ch. C, 0x4xx = Ch. D)                                                              |

| Serial Slave Mode (SCS = 1)                       | (0x000) Summation Mode Control                                                                            |

| Serial Data Framing                               | (0x001) Sync Mode Control                                                                                 |

| Self-Framing Mode15External Framing Mode15        | (0x002) BIST Counter       36         (0x003) BIST Result       38                                        |

| Serial Port Cascade Configuration                 | (0xn00) Start Update Hold-Off Counter                                                                     |

| Serial Data Format                                | (0xn01) NCO Control                                                                                       |

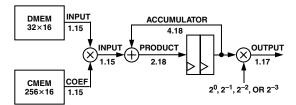

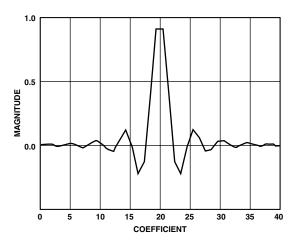

| PROGRAMMABLE RAM COEFFICIENT FILTER (RCF)         | (0xn02) NCO Frequency                                                                                     |

| OVERVIEW OF THE RCF BLOCKS                        | (0xn03) NCO Frequency Update Hold-Off Counter                                                             |

| INTERPOLATING FIR FILTER                          | (0xn04) NCO Phase Offset                                                                                  |

| Channel A RCF Control Registers                   | (0xn05) NCO Phase Offset Update Hold-Off Counter                                                          |

| PSK MODULATOR                                     | (0xn06) CIC Scale                                                                                         |

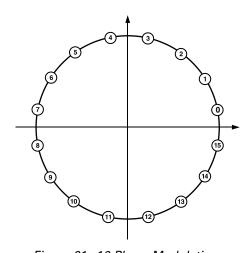

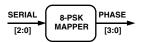

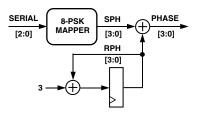

| 8-PSK Modulation 21                               | (0xn08) CIC2 Decimation – 1 ( $M_{CIC2}$ – 1)                                                             |

| $3\pi/8$ -8-PSK Modulation                        | (0xn09) CIC5 Interpolation                                                                                |

| MSK Look-Up Table                                 | (0xn0A) Number of RCF Coefficients – 1                                                                    |

| GMSK Look-Up Table                                | (0xn0B) RCF Coefficient Offset                                                                            |

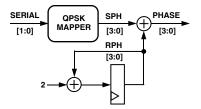

| QPSK Look-Up Table                                | (0xn0C) Channel Mode Control 1                                                                            |

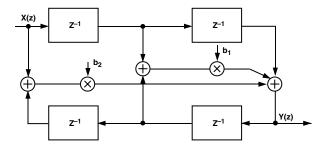

| PHASE EQUALIZER                                   | (0xn0D) Channel Mode Control 2                                                                            |

| FINE SCALE AND RAMP                               | (0xn0E) Fine Scale Factor                                                                                 |

| FINE SCALING                                      | (0xn0F) RCF Time Slot Sync         40           (0xn10-0xn11) RCF Phase Equalizer Coefficients         40 |

| Ramp Triggering                                   | (0xn12-0xn11) KCF Flase Equalizer Coefficients                                                            |

| Special Handling for SYNC0 Pin-Sync               | (0xn16) Serial Port Setup                                                                                 |

| CASCADED INTERGRATOR COMB (CIC)                   | (0xn17) Power Ramp Length 0                                                                               |

| INTERPOLATING FILTERS                             | (0xn18) Power Ramp Length 1                                                                               |

| CIC Scaling                                       | (0xn19) Power Ramp Rest Time                                                                              |

| CIC5                                              | (0xn20-0xn1F) Unused                                                                                      |

| The rCIC2 RESAMPLING INTERPOLATION FILTER         | (0xn20-0xn3F) Data Memory                                                                                 |

| Permissible Values of $L_{rCIC2}$ and $M_{rCIC2}$ | (0xn80–0xnFF) Coefficient Memory                                                                          |

| Programming Guidelines for AD6623 CIC Filters     | PSEUDOCODE                                                                                                |

| NUMERICALLY CONTROLLED OSCILLATOR/TUNER (NCO)27   | Write Pseudocode                                                                                          |

| Phase Dither                                      | Read Pseudocode4                                                                                          |

| Amplitude Dither                                  | AD6623 EVALUATION PCB AND SOFTWARE                                                                        |

| Phase Offset                                      | APPLICATIONS                                                                                              |

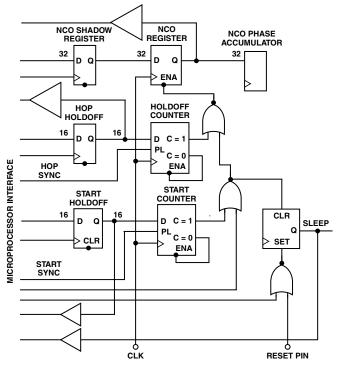

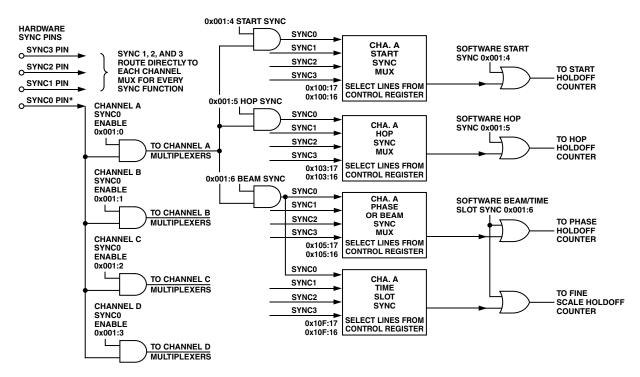

| NCO Frequency Update and Phase Offset             | Using the AD6623 to Process UMTS Carriers                                                                 |

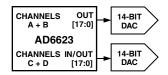

| Update Hold-Off Counters                          | Digital-to-Analog Converter (DAC) Selection                                                               |

| SUMMATION BLOCK                                   | Determining the Number of TSPs to Use                                                                     |

| Dual 18-Bit Output Configuration                  | Programming Multiple TSPs                                                                                 |

| Output Data Format                                | Driving Multiple TSP Serial Ports                                                                         |

| Output Clip Detection                             | USING THE AD6623 TO PROCESS TWO UMTS CARRIERS                                                             |

| Cascading Multiple AD6623s                        | WITH 24× OUTPUT RATE                                                                                      |

| Selection of Real and Complex Data Types          | Overview                                                                                                  |

| SYNCHRONIZATION                                   | Configuring the AD6623                                                                                    |

| Hold-Off Counters and Shadow Registers            | AD6623 Register Configuration                                                                             |

| Start with No Sync                                | OUTLINE DIMENSIONS 4'                                                                                     |

|                                                   | Revision History 4                                                                                        |

-2- REV. A

#### PRODUCT DESCRIPTION

The AD6623 is a 4-channel Transmit Signal Processor (TSP) that creates high bandwidth data for Transmit Digital-to-Analog Converters (TxDACs) from baseband data provided by a Digital Signal Processor (DSP). Modern TxDACs have achieved sufficiently high sampling rates, analog bandwidth, and dynamic range to create the first Intermediate Frequency (IF) directly. The AD6623 synthesizes multicarrier and multistandard digital signals to drive these TxDACs. The RAM-based architecture allows easy reconfiguration for multimode applications. Modulation, pulse-shaping and anti-imaging filters, static equalization, and tuning functions are combined in a single, cost-effective device. Digital IF signal processing provides repeatable manufacturing, higher accuracy, and more flexibility than comparable high dynamic range analog designs.

The AD6623 has four identical digital TSPs complete with synchronization circuitry and cascadable wideband channel summation. AD6623 is pin compatible to AD6622 and can operate in AD6622-compatible control register mode. The AD6623 utilizes a 3.3 V I/O power supply and a 2.5 V core power supply. All I/O pins are 5 V tolerant. All control registers and coefficient values are programmed through a generic microprocessor interface. Intel and Motorola microprocessor bus modes are supported. All inputs and outputs are LVCMOS compatible.

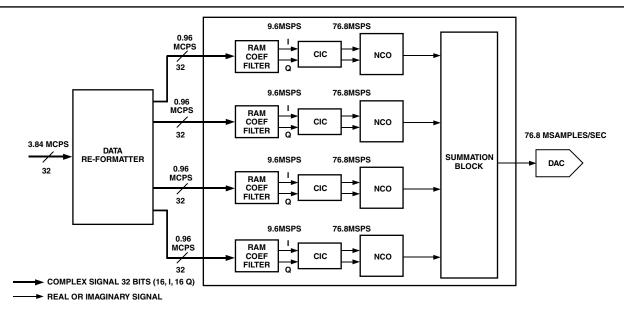

#### **FUNCTIONAL OVERVIEW**

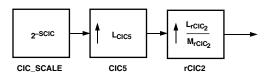

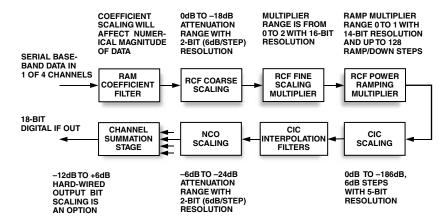

Each TSP has five cascaded signal processing elements: a programmable interpolating RAM Coefficient Filter (RCF), a programmable Scale and Power Ramp, a programmable fifth order Cascaded Integrator Comb (CIC5) interpolating filter, a flexible second order Resampling Cascaded Integrator Comb filter (rCIC2), and a Numerically Controlled Oscillator/Tuner (NCO).

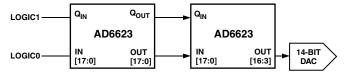

The outputs of the four TSPs are summed and scaled on-chip. In multicarrier wideband transmitters, a bidirectional bus allows the Parallel (wideband) IF Input/Output to drive a second DAC. In this operational mode two AD6623 channels drive one DAC and the other two AD6623 channels drive a second DAC. Multiple AD6623s may be combined by driving the INOUT[17:0] of the succeeding with the OUT[17:0] of the preceding chip. The

INOUT[17:0] can alternatively be masked off by software to allow preceding AD6623's outputs to be ignored.

Each channel accepts input data from independent serial ports that may be connected directly to the serial port of Digital Signal Processor (DSP) chips.

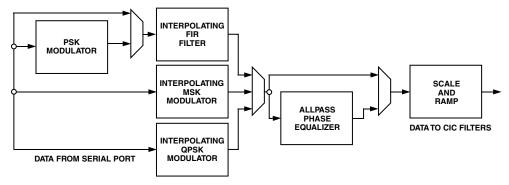

The RCF implements any one of the following functions: Interpolating Finite Impulse Response (FIR) filter,  $\pi/4$ -DQPSK modulator, 8-PSK modulator, or  $3\pi/8$ -8-PSK modulator, GMSK modulator, and QPSK modulator. Each AD6623 channel can be dynamically switched between the GMSK modulation mode and the  $3\pi/8$ -8-PSK modulation mode in order to support the GSM/EDGE standard. The RCF also implements an Allpass Phase Equalizer (APE) which meets the requirements of IS-95-A/B standard (CDMA transmission).

The programmable Scale and Power Ramp block allows power ramping on a time-slot basis as specified for some air-interface standards (e.g., GSM, EDGE). A fine scaling unit at the programmable FIR filter output allows an easy signal amplitude level adjustment on time slot basis.

The CIC5 provides integer rate interpolation from 1 to 32 and coarse anti-image filtering. The rCIC2 provides fractional rate interpolation from 1 to 4096 in steps of 1/512. The wide range of interpolation factors in each CIC filter stage and a highly flexible resampler incorporated into rCIC2 makes the AD6623 useful for creating both narrowband and wideband carriers in a high-speed sample stream.

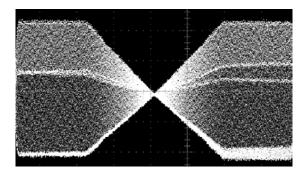

The high resolution 32-bit NCO allows flexibility in frequency planning and supports both digital and analog air interface standards. The high speed NCO tunes the interpolated complex signal from the rCIC2 to an IF channel. The result may be real or complex. Multicarrier phase synchronization pins and phase offset registers allow intelligent management of the relative phase of independent RF channels. This capability supports the requirements for phased array antenna architectures and management of the wideband peak/power ratio to minimize clipping at the DAC.

The wideband Output Ports can deliver real or complex data. Complex words are interleaved into real (I) and imaginary (Q) parts at half the master clock rate.

REV. A -3-

# AD6623—SPECIFICATIONS

# RECOMMENDED OPERATING CONDITIONS

|               | Test  | AD6623 |     |      |      |

|---------------|-------|--------|-----|------|------|

| Parameter     | Level | Min    | Тур | Max  | Unit |

| VDD           | IV    | 2.25   | 2.5 | 2.75 | V    |

| VDDIO         | IV    | 3.0    | 3.3 | 3.6  | V    |

| $T_{AMBIENT}$ | IV    | -40    | +25 | +85  | °C   |

# **ELECTRICAL CHARACTERISTICS**

| Parameter (Conditions)                           | Temp | Test Level | Min  | Typ           | Max  | Unit |

|--------------------------------------------------|------|------------|------|---------------|------|------|

| LOGIC INPUTS (5 V TOLERANT)                      |      |            |      |               |      |      |

| Logic Compatibility                              | Full |            |      | 3.3 V CMOS    |      |      |

| Logic "1" Voltage                                | Full | IV         | 2.0  |               | 5.0  | V    |

| Logic "0" Voltage                                | Full | IV         | -0.3 |               | +0.8 | V    |

| Logic "1" Current                                | Full | IV         |      | 1             | 10   | μA   |

| Logic "0" Current                                | Full | IV         |      | 0             | 10   | μA   |

| Input Capacitance                                | 25°C | V          |      | 4             |      | pF   |

| LOGIC OUTPUTS                                    |      |            |      |               |      |      |

| Logic Compatibility                              | Full |            |      | 3.3 V CMOS/TT | L    |      |

| Logic "1" Voltage ( $I_{OH} = 0.25 \text{ mA}$ ) | Full | IV         | 2.0  | VDD - 0.2     |      | V    |

| Logic "0" Voltage ( $I_{OL} = 0.25 \text{ mA}$ ) | Full | IV         |      | 0.2           | 0.4  | V    |

| IDD SUPPLY CURRENT                               |      |            |      |               |      |      |

| GSM Example: CORE                                |      | V          |      | 232           |      | mA   |

| I/O                                              |      |            |      | 56            |      | mA   |

| IS-136 Example: CORE                             |      | V          |      | 207           |      | mA   |

| I/O                                              |      |            |      | 55            |      | mA   |

| WBCDMA Example                                   |      | V          |      | TBD           |      | mA   |

| Sleep Mode                                       | Full | IV         |      | TBD           |      | mA   |

| POWER DISSIPATION                                |      |            |      |               |      |      |

| GSM Example                                      |      | V          |      | 740           |      | mW   |

| IS-136 Example                                   |      | V          |      | 700           |      | mW   |

| WBCDMA Example                                   |      | V          |      | TBD           |      | mW   |

| Sleep Mode                                       | Full | IV         |      | TBD           |      | mW   |

See the Thermal Management section of the data sheet for further details.

-4- REV. A

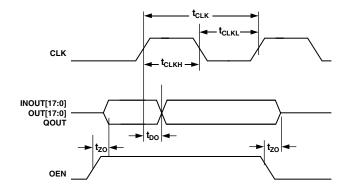

# GENERAL TIMING CHARACTERISTICS<sup>1, 2</sup>

|                                    |                                                     |              | Test     |      | AD6623AS          | <u> </u> |          |

|------------------------------------|-----------------------------------------------------|--------------|----------|------|-------------------|----------|----------|

| Parameter (                        | Parameter (Conditions)                              |              | Level    | Min  | Typ               | Max      | Unit     |

| CLK Timing                         | Requirements:                                       |              |          |      |                   |          |          |

| t <sub>CLK</sub>                   | CLK Period                                          | Full         | I        | 9.6  |                   |          | ns       |

| t <sub>CLKL</sub>                  | CLK Width Low                                       | Full         | IV       | 3    |                   |          | ns       |

| t <sub>CLKH</sub>                  | CLK Width High                                      | Full         | IV       | 3    | $0.5 \times t_0$  | CLK      | ns       |

|                                    | ng Requirement:                                     |              |          |      |                   | -        |          |

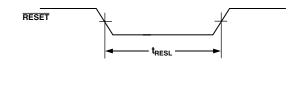

| t <sub>resl</sub>                  | RESET Width Low                                     | Full         | I        | 30.0 |                   |          | ns       |

|                                    | iming Requirements:                                 |              |          |      |                   |          |          |

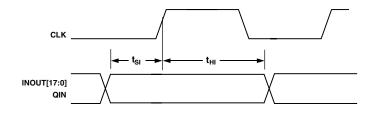

| _                                  | INOUT[17:0], QIN to ↑CLK Setup Time                 | Full         | IV       | 1    |                   |          | ns       |

| t <sub>SI</sub><br>t <sub>HI</sub> | INOUT[17:0], QIN to \CLK Hold Time                  | Full         | IV       | 2    |                   |          | ns       |

|                                    |                                                     | Tun          |          | 2    |                   |          | 110      |

| =                                  | Timing Characteristics:                             |              |          |      |                   |          |          |

| $t_{\mathrm{DO}}$                  | ↑CLK to OUT[17:0], INOUT[17:0],                     | F 11         | 75.7     |      |                   | (        |          |

|                                    | QOUT Output Delay Time                              | Full         | IV       | 2    |                   | 6        | ns       |

| $t_{ m DZO}$                       | OEN HIGH to OUT[17:0] Active                        | Full         | IV       | 3    |                   | 7.5      | ns       |

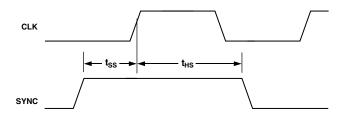

| SYNC Timing                        | g Requirements:                                     |              |          |      |                   |          |          |

| $t_{\mathrm{SS}}$                  | SYNC(0, 1, 2, 3) to $\uparrow$ CLK Setup Time       | Full         | IV       | 1    |                   |          | ns       |

| t <sub>HS</sub>                    | SYNC(0, 1, 2, 3) to $\uparrow$ CLK Hold Time        | Full         | IV       | 2    |                   |          | ns       |

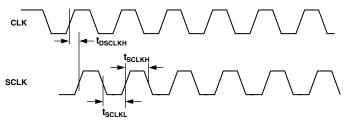

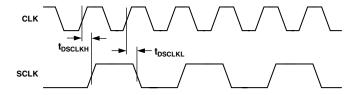

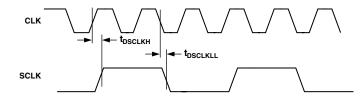

| Master Mode                        | Serial Port Timing Requirements (SCS = 0):          |              |          |      |                   |          |          |

| Switching Ch                       |                                                     |              |          |      |                   |          |          |

| t <sub>DSCLK1</sub>                | ↑CLK to ↑SCLK Delay (divide by 1)                   | Full         | IV       | 4    |                   | 10.5     | ns       |

| DSCLKH                             | ↑CLK to ↑SCLK Delay (for any other divisor)         | Full         | IV       | 5    |                   | 13       | ns       |

| t <sub>DSCLKL</sub>                | ↑CLK to ↓SCLK Delay                                 |              |          |      |                   |          |          |

|                                    | (divide by 2 or even number)                        | Full         | IV       | 3.5  |                   | 9        | ns       |

| t <sub>DSCLKLL</sub>               | ↓CLK to ↓SCLK Delay                                 |              |          |      |                   |          |          |

|                                    | (divide by 3 or odd number)                         | Full         | IV       | 4    |                   | 10       | ns       |

|                                    | Channel is Self-Framing                             |              |          |      |                   |          |          |

| $t_{\mathrm{SSDI0}}$               | SDIN to ↑SCLK Setup Time                            | Full         | IV       | 1.7  |                   |          | ns       |

| $t_{\mathrm{HSDI0}}$               | SDIN to \SCLK Hold Time                             | Full         | IV       | 0    |                   | 2 =      | ns       |

| t <sub>DSFO0A</sub>                | ↑SCLK to SDFO Delay                                 | Full         | IV       | 0.5  |                   | 3.5      | ns       |

|                                    | Channel is External-Framing                         | T11          | 13.7     |      |                   |          |          |

| t <sub>SSFI0</sub>                 | SDFI to ↑SCLK Setup Time<br>SDFI to ↑SCLK Hold Time | Full         | IV<br>IV | 2    |                   |          | ns       |

| t <sub>HSFI0</sub>                 | SDIN to \SCLK Hold Time SDIN to \SCLK Setup Time    | Full<br>Full | IV       | 0    |                   |          | ns       |

| SSDI0                              | SDIN to \SCLK Setup Time SDIN to \SCLK Hold Time    | Full         | IV       | 2 0  |                   |          | ns       |

| t <sub>HSDI0</sub>                 | ↑SCLK to SDFO Delay                                 | Full         | IV       | 0.5  |                   | 3        | ns<br>ns |

| t <sub>DSFO0B</sub>                | <u> </u>                                            | Tull         | 1 V      | 0.5  |                   |          | 115      |

|                                    | Terial Port Timing Requirements (SCS = 1):          |              |          |      |                   |          |          |

| Switching Ch                       |                                                     | F11          | 13.7     |      | 2 ** :            |          |          |

| t <sub>SCLK</sub>                  | SCLK Period                                         | Full         | IV       | 2.5  | $2 \times t_{CI}$ | .K       | ns       |

| t <sub>SCLKL</sub>                 | SCLK Low Time                                       | Full         | IV       | 3.5  |                   |          | ns       |

| t <sub>SCLKH</sub>                 | SCLK High Time<br>Channel is Self-Framing           | Full         | IV       | 3.5  |                   |          | ns       |

| _                                  | SDIN to \(^\SCLK\) Setup Time                       | E11          | IV       | 1    |                   |          |          |

| t <sub>SSDH</sub>                  | SDIN to \SCLK Setup Time SDIN to \SCLK Hold Time    | Full<br>Full | IV<br>IV | 2.5  |                   |          | ns       |

| t <sub>HSDH</sub>                  | ↑SCLK to SDFO Delay                                 | Full         | IV       | 4    |                   | 10       | ns       |

| t <sub>DSFO1</sub>                 | Channel is External-Framing                         | 1 uii        | 1 1      | 4    |                   | 10       | ns       |

| t                                  | SDFI to \(^\)SCLK Setup Time                        | Full         | IV       | 2    |                   |          | ne       |

| SSFI1                              | SDFI to \SCLK Setup Time SDFI to \SCLK Hold Time    | Full         | IV       | 1    |                   |          | ns       |

| HSFII                              | SDIN to \SCLK Setup Time                            | Full         | IV       | 1    |                   |          | ns<br>ns |

| t <sub>SSDI1</sub>                 | SDIN to \SCLK Setup Time SDIN to \SCLK Hold Time    | Full         | IV       | 2.5  |                   |          | ns       |

| t <sub>HSDI1</sub>                 | ↓SCLK to SDFO Delay                                 | Full         | IV       | 10   |                   |          | ns       |

| t <sub>DSFO1</sub><br>NOTES        | VOCEIX to ODITO Delay                               | 1 uii        | 1 4      | 10   |                   |          | 112      |

Specifications subject to change without notice.

REV. A -5-

NOTES

1 All Timing Specifications valid over VDD range of 2.375 V to 2.675 V and VDDIO range of 3.0 V to 3.6 V.

2 C<sub>LOAD</sub> = 40 pF on all outputs (unless otherwise specified).

3 The timing parameters for SCLK, SDIN, SDFI, SDFO, and SYNC apply to all four channels (A, B, C, and D).

# MICROPROCESSOR PORT TIMING CHARACTERISTICS<sup>1, 2</sup>

|                   |                                                                                                     |      | Test  |                    | AD6623                    | AS                            |      |

|-------------------|-----------------------------------------------------------------------------------------------------|------|-------|--------------------|---------------------------|-------------------------------|------|

| Parameter (C      | Conditions)                                                                                         | Temp | Level | Min                | Typ                       | Max                           | Unit |

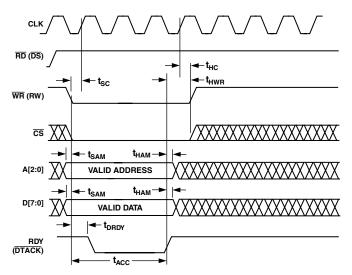

| MICROPRO          | CESSOR PORT, MODE INM (MODE = 0)                                                                    |      |       |                    |                           |                               |      |

| MODE INM          | Write Timing:                                                                                       |      |       |                    |                           |                               |      |

| $t_{SC}$          | Control <sup>3</sup> to ↑CLK Setup Time                                                             | Full | IV    | 4.5                |                           |                               | ns   |

| $t_{HC}$          | Control <sup>3</sup> to ↑CLK Hold Time                                                              | Full | IV    | 2.0                |                           |                               | ns   |

| $t_{HWR}$         | $\overline{WR}(RW)$ to $RDY(\overline{DTACK})$ Hold Time                                            | Full | IV    | 8.0                |                           |                               | ns   |

| $t_{SAM}$         | Address/Data to $\overline{WR}(RW)$ Setup Time                                                      | Full | IV    | 3.0                |                           |                               | ns   |

| $t_{HAM}$         | Address/Data to RDY(\overline{DTACK}) Hold Time                                                     | Full | IV    | 2.0                |                           |                               | ns   |

| $t_{DRDY}$        | $\overline{WR}(RW)$ to $RDY(\overline{DTACK})$ Delay                                                | Full | IV    | 4.0                |                           |                               | ns   |

| $t_{ACC}$         | $\overline{WR}(RW)$ to $RDY(\overline{DTACK})$ High Delay                                           | Full | IV    | $4 \times t_{CLK}$ | $5 \times t_{CLK}$        | $9 \times t_{CLK}$            | ns   |

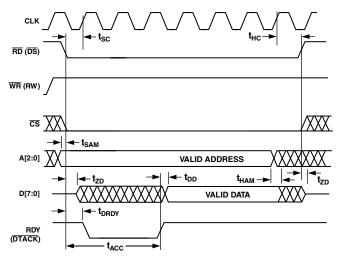

| MODE INM I        | Read Timing:                                                                                        |      |       |                    |                           |                               |      |

| $t_{SC}$          | Control <sup>3</sup> to ↑CLK Setup Time                                                             | Full | IV    | 4.5                |                           |                               | ns   |

| $t_{HC}$          | Control <sup>3</sup> to ↑CLK Hold Time                                                              | Full | IV    | 2.0                |                           |                               | ns   |

| $t_{SAM}$         | Address to $\overline{RD}(\overline{DS})$ Setup Time                                                | Full | IV    | 3.0                |                           |                               | ns   |

| $t_{HAM}$         | Address to Data Hold Time                                                                           | Full | IV    | 2.0                |                           |                               | ns   |

| $t_{ZOZ}$         | Data Three-State Delay                                                                              | Full | IV    |                    |                           |                               | ns   |

| $t_{DD}$          | RDY( <del>DTACK</del> ) to Data Delay                                                               | Full | IV    |                    |                           |                               | ns   |

| $t_{DRDY}$        | $\overline{RD}(\overline{DS})$ to $\overline{RDY}(\overline{DTACK})$ Delay                          | Full | IV    | 4.0                |                           |                               | ns   |

| $t_{ACC}$         | $\overline{RD}(\overline{DS})$ to $RDY(\overline{DTACK})$ High Delay                                | Full | IV    | $8 \times t_{CLK}$ | $10 \times t_{CL}$        | $_{\rm K}$ 13 × $t_{\rm CLK}$ | ns   |

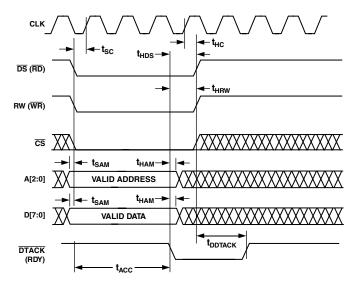

| MICROPRO          | CESSOR PORT, MOTOROLA (MODE = 1)                                                                    |      |       |                    |                           |                               |      |

| MODE MNM          | Write Timing:                                                                                       |      |       |                    |                           |                               |      |

| $t_{SC}$          | Control <sup>3</sup> to ↑CLK Setup Time                                                             | Full | IV    | 4.5                |                           |                               | ns   |

| $t_{HC}$          | Control <sup>3</sup> to ↑CLK Hold Time                                                              | Full | IV    | 2.0                |                           |                               | ns   |

| $t_{HDS}$         | $\overline{DS}(\overline{RD})$ to $\overline{DTACK}(RDY)$ Hold Time                                 | Full | IV    | 8.0                |                           |                               | ns   |

| $t_{HRW}$         | $RW(\overline{WR})$ to $\overline{DTACK}(RDY)$ Hold Time                                            | Full | IV    | 8.0                |                           |                               | ns   |

| t <sub>SAM</sub>  | Address/Data to $RW(\overline{WR})$ Setup Time                                                      | Full | IV    | 3.0                |                           |                               | ns   |

| $t_{HAM}$         | Address/Data to $RW(\overline{WR})$ Hold Time                                                       | Full | IV    | 2.0                |                           |                               | ns   |

| $t_{DDTACK}$      | $\overline{\mathrm{DS}}(\overline{\mathrm{RD}})$ to $\overline{\mathrm{DTACK}}(\mathrm{RDY})$ Delay |      |       |                    |                           |                               | ns   |

| $t_{ACC}$         | $RW(\overline{WR})$ to $\overline{DTACK}(RDY)$ Low Delay                                            | Full | IV    | $4 \times t_{CLK}$ | $5 \times t_{\text{CLK}}$ | $9 \times t_{CLK}$            | ns   |

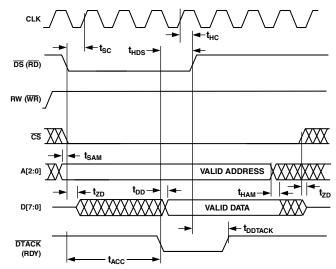

| MODE MNM          | Read Timing:                                                                                        |      |       |                    |                           |                               |      |

| $t_{SC}$          | Control <sup>3</sup> to ↑CLK Setup Time                                                             | Full | IV    | 4.0                |                           |                               | ns   |

| $t_{HC}$          | Control <sup>3</sup> to ↑CLK Hold Time                                                              | Full | IV    | 2.0                |                           |                               | ns   |

| t <sub>HDS</sub>  | $\overline{DS}(\overline{RD})$ to $\overline{DTACK}(RDY)$ Hold Time                                 | Full | IV    | 8.0                |                           |                               | ns   |

| $t_{SAM}$         | Address to $\overline{DS}(\overline{RD})$ Setup Time                                                | Full | IV    | 3.0                |                           |                               | ns   |

| t <sub>HAM</sub>  | Address to Data Hold Time                                                                           | Full | IV    | 2.0                |                           |                               | ns   |

| $t_{\mathrm{ZD}}$ | Data Three-State Delay                                                                              | Full | IV    |                    |                           |                               | ns   |

| t <sub>DD</sub>   | DTACK(RDY) to Data Delay                                                                            | Full | IV    |                    |                           |                               | ns   |

| $t_{DDTACK}$      | $\overline{\rm DS}(\overline{\rm RD})$ to $\overline{\rm DTACK}({\rm RDY})$ Delay                   | Full | IV    |                    |                           |                               | ns   |

| $t_{ACC}$         | $\overline{DS}(\overline{RD})$ to $\overline{DTACK}(RDY)$ Low Delay                                 | Full | IV    | $8 \times t_{CLK}$ | $10 \times t_{CL}$        | $_{\rm K}$ 13 × $t_{\rm CLK}$ | ns   |

| NOTES             |                                                                                                     |      | •     |                    |                           |                               |      |

Specifications subject to change without notice.

REV. A -6-

NOTES

<sup>1</sup>All Timing Specifications valid over VDD range of 2.375 V to 2.675 V and VDDIO range of 3.0 V to 3.6 V.

<sup>&</sup>lt;sup>2</sup>C<sub>LOAD</sub> = 40 pF on all outputs (unless otherwise specified). <sup>3</sup>Specification pertains to control signals: RW,  $(\overline{WR})$ ,  $\overline{DS}$ ,  $(\overline{RD})$ ,  $\overline{CS}$ .

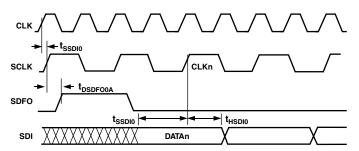

#### **TIMING DIAGRAMS**

Figure 1. Parallel Output Switching Characteristics

Figure 4. RESET Timing Requirements

Figure 2. Wideband Input Timing

Figure 5. SCLK Switching Characteristics (Divide by 1)

Figure 3. SYNC Timing Inputs

Figure 6. SCLK Switching Characteristic (Divide by 2 or EVEN Integer)

Figure 7. SCLK Switching Characteristic (Divide by 3 or ODD Integer)

REV. A -7-

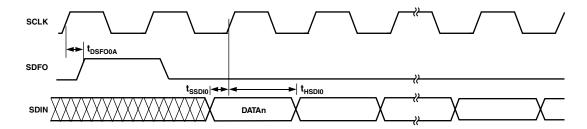

Figure 8. Serial Port Timing, Master Mode (SCS = 0), Channel is Self-Framing

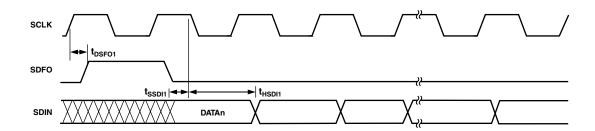

Figure 9. Serial Port Timing, Slave Mode (SCS = 1), Channel is Self-Framing

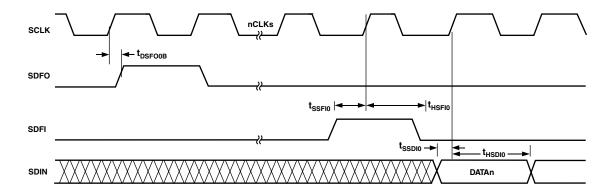

Figure 10. Serial Port Timing, Master Mode (SCS = 0), Channel is External-Framing

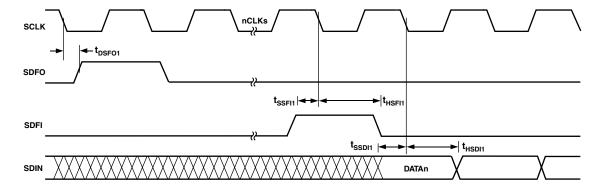

Figure 11. Serial Port Timing, Slave Mode (SCS = 1), Channel is External-Framing

#### TIMING DIAGRAMS—INM MICROPORT MODE

#### NOTES

- 1.  $t_{ACC}$  access time depends on the address accessed. Access time is measured from Fe of  $\overline{WR}$  to the Re of Rdy.

- 2.  $t_{\mbox{\scriptsize ACC}}$  REQUIRES A MAXIMUM 9 CLK PERIODS.

Figure 12. INM Microport Write Timing Requirements

#### NOTES

- 1.  $t_{ACC}$  ACCESS TIME DEPENDS ON THE ADDRESS ACCESSED. ACCESS TIME IS MEASURED FROM FE OF  $\overline{WR}$  TO THE RE OF RDY.

- 2.  $t_{ACC}$  REQUIRES A MAXIMUM OF 13 CLK PERIODS AND APPLIES TO A[2:0] = 7, 6, 5, 3, 2, 1

Figure 13. INM Microport Read Timing Requirements

#### TIMING DIAGRAMS—MNM MICROPORT MODE

#### NOTES

- 1.  $t_{ACC}$  ACCESS TIME DEPENDS ON THE ADDRESS ACCESSED. ACCESS TIME IS MEASURED FROM FE OF  $\overline{DS}$  TO THE FE OF  $\overline{DTACK}$ .

- 2. t<sub>ACC</sub> REQUIRES A MAXIMUM 9 CLK PERIODS.

Figure 14. MNM Microport Write Timing Requirements

#### NOTES

- 1.  $t_{ACC}$  access time depends on the address accessed. Access time is measured from Fe of  $\overline{DS}$  to the Fe of  $\overline{DTACK}$ .

- 2. t<sub>ACC</sub> REQUIRES A MAXIMUM 13 CLK PERIODS.

Figure 15. MNM Microport Read Timing Requirements

REV. A -9-

#### **ABSOLUTE MAXIMUM RATINGS\***

| VDDIO                                             |

|---------------------------------------------------|

| VDD                                               |

| Input Voltage $-0.3~V$ to +5 $V$ (5 $V$ Tolerant) |

| Output Voltage Swing0.3 V to VDDIO + 0.3 V        |

| Load Capacitance 200 pF                           |

| Junction Temperature Under Bias 125°C             |

| Operating Temperature40°C to +85°C (Ambient)      |

| Storage Temperature Range65°C to +150°C           |

| Lead Temperature (5 sec) $\dots 280^{\circ}C$     |

|                                                   |

<sup>\*</sup>Stresses greater than those listed above may cause permanent damage to the device. These are stress ratings only; functional operation of the devices at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS

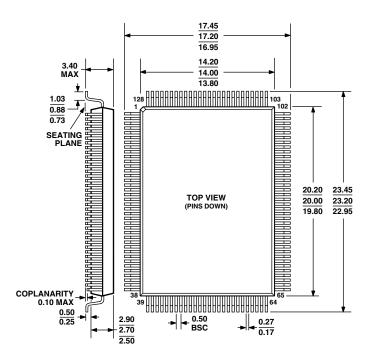

128-Lead MQFP with Internal Heat Spreader:

$\theta_{IA} = 28.1^{\circ}\text{C/W}$ , no airflow

$\theta_{IA} = 22.6$ °C/W, 200 lfpm airflow

$\theta_{IA} = 20.5$ °C/W, 400 lfpm airflow

#### 196-Lead BGA:

$\theta_{JA} = 26.3^{\circ}$ C/W, no airflow

$\theta_{IA} = 22^{\circ}\text{C/W}$ , 200 lfpm airflow

Thermal measurements made in the horizontal position on a 4-layer board.

#### **EXPLANATION OF TEST LEVELS**

- I. 100% Production Tested

- II. 100% Production Tested at 25°C, and Sample Tested at Specified Temperatures

- III. Sample Tested Only

- IV. Parameter Guaranteed by Design and Analysis

- V. Parameter is Typical Value Only

#### **ORDERING GUIDE**

| Model        | Temperature Range        | Package Description                                  | Package Option |

|--------------|--------------------------|------------------------------------------------------|----------------|

| AD6623AS     | –40°C to +85°C (Ambient) | 128-Lead MQFP (Plastic Quad Flatpack)                | S-128          |

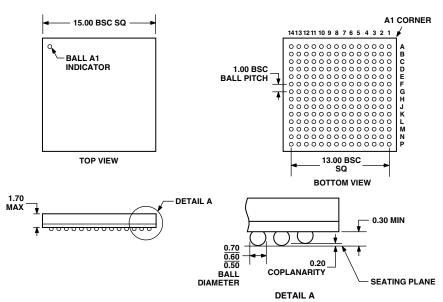

| AD6623ABC    | -40°C to +85°C (Ambient) | 196-Lead CSPBGA (Chip Scale Package Ball Grid Array) | BC-196         |

| AD6623S/PCB  |                          | MQFP Evaluation Board with AD6623 and Software       |                |

| AD6623BC/PCB |                          | CSPBGA Evaluation Board with AD6623 and Software     |                |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD6623 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-10- REV. A

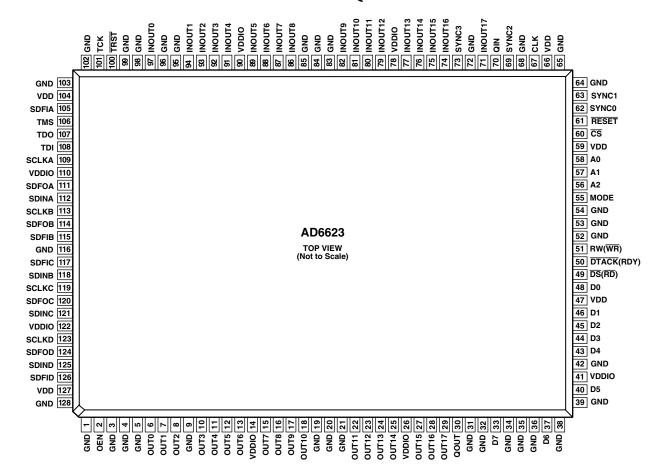

# PIN CONFIGURATION 128-Lead MQFP

REV. A –11–

#### 128-LEAD FUNCTION DESCRIPTIONS

| Pin Number                                                                                                   | Mnemonic                                          | Type  | Description                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------|

| 1, 3–5, 9, 19–21, 31, 32, 34–36, 38, 39, 42, 52–54, 64–65, 68, 72, 83–85, 95, 96, 98, 99, 102, 103, 116, 128 | GND                                               | P     | Ground Connection                                                                                                                |

| 2                                                                                                            | OEN <sup>1</sup>                                  | I     | Active High Output Enable Pin                                                                                                    |

| 29, 28, 27, 25, 24, 23, 22, 18, 17, 16, 15, 13, 12, 11, 10, 8, 7, 6                                          | OUT[17:0]                                         | O/T   | Parallel Output Data                                                                                                             |

| 47, 59, 66, 104, 127                                                                                         | VDD                                               | P     | 2.5 V Supply                                                                                                                     |

| 14, 26, 41, 78, 90, 110, 122                                                                                 | VDDIO                                             | P     | 3.3 V Supply                                                                                                                     |

| 30                                                                                                           | QOUT                                              | O/T   | When HIGH indicates Q Output Data (Complex Output Mode)                                                                          |

| 33, 37, 40, 43, 44, 45, 46, 48                                                                               | D[7:0]                                            | I/O/T | Bidirectional Microport Data                                                                                                     |

| 49                                                                                                           | $\overline{\text{DS}}$ ( $\overline{\text{RD}}$ ) | I     | INM Mode: Read Signal, MNM Mode: Data Strobe Signal                                                                              |

| 50                                                                                                           | DTACK (RDY)                                       |       | Acknowledgment of a Completed Transaction (Signals when µP Port Is Ready for an Access) Open Drain, Must Be Pulled Up Externally |

| 51                                                                                                           | $RW(\overline{WR})$                               | I     | Active HIGH Read, Active Low Write                                                                                               |

| 55                                                                                                           | MODE                                              | I     | Sets Microport Mode: MODE = 1, MNM Mode;<br>MODE = 0, INM Mode                                                                   |

| 56, 57, 58                                                                                                   | A[2:0]                                            | I     | Microport Address Bus                                                                                                            |

| 60                                                                                                           | CS                                                | I     | Chip Select, Active low enable for µP Access                                                                                     |

| 61                                                                                                           | $\overline{\text{RESET}}^2$                       | Ι     | Active Low Reset Pin                                                                                                             |

| 62                                                                                                           | SYNC01                                            | Ι     | SYNC Signal for Synchronizing Multiple AD6623s                                                                                   |

| 63                                                                                                           | SYNC1 <sup>1</sup>                                | Ι     | SYNC Signal for Synchronizing Multiple AD6623s                                                                                   |

| 67                                                                                                           | CLK <sup>1</sup>                                  | I     | Input Clock                                                                                                                      |

| 69                                                                                                           | SYNC2 <sup>1</sup>                                | I     | SYNC Signal for Synchronizing Multiple AD6623s                                                                                   |

| 70                                                                                                           | QIN <sup>1</sup>                                  | Ι     | When HIGH indicates Q input data (Complex Input Mode)                                                                            |

| 71, 74–77, 79–82, 86–89, 91–94, 97                                                                           | INOUT[17:0] <sup>1</sup>                          | I/O   | Wideband Input/Output Data (Allows Cascade of Multiple AD6623 Chips In a System)                                                 |

| 73                                                                                                           | SYNC3 <sup>1</sup>                                | Ι     | SYNC Signal for Synchronizing Multiple AD6623s                                                                                   |

| 100                                                                                                          | $\overline{TRST}^2$                               | I     | Test Reset Pin                                                                                                                   |

| 101                                                                                                          | TCK <sup>1</sup>                                  | I     | Test Clock Input                                                                                                                 |

| 105                                                                                                          | SDFIA                                             | I     | Serial Data Frame Input—Channel A                                                                                                |

| 106                                                                                                          | TMS <sup>2</sup>                                  | I     | Test Mode Select                                                                                                                 |

| 107                                                                                                          | TDO                                               | O     | Test Data Output                                                                                                                 |

| 108                                                                                                          | $TDI^1$                                           | I     | Test Data Input                                                                                                                  |

| 109                                                                                                          | SCLKA                                             | I/O   | Bidirectional Serial Clock—Channel A                                                                                             |

| 111                                                                                                          | SDFOA                                             | O     | Serial Data Frame Sync Output—Channel A                                                                                          |

| 112                                                                                                          | SDINA <sup>1</sup>                                | Ι     | Serial Data Input—Channel A                                                                                                      |

| 113                                                                                                          | SCLKB                                             | I/O   | Bidirectional Serial Clock—Channel B                                                                                             |

| 114                                                                                                          | SDFOB                                             | O     | Serial Data Frame Sync Output—Channel B                                                                                          |

| 115                                                                                                          | SDFIB                                             | I     | Serial Data Frame Input —Channel B                                                                                               |

| 117                                                                                                          | SDFIC                                             | I     | Serial Data Frame Input—Channel C                                                                                                |

| 118                                                                                                          | SDINB <sup>1</sup>                                | I     | Serial Data Input—Channel B                                                                                                      |

| 119                                                                                                          | SCLKC                                             | I/O   | Bidirectional Serial Clock—Channel C                                                                                             |

| 120                                                                                                          | SDFOC                                             | O     | Serial Data Frame Sync Output—Channel C                                                                                          |

| 121                                                                                                          | SDINC <sup>1</sup>                                | I     | Serial Data Input—Channel C                                                                                                      |

| 123                                                                                                          | SCLKD                                             | I/O   | Bidirectional Serial Clock—Channel D                                                                                             |

| 124                                                                                                          | SDFOD                                             | 0     | Serial Data Frame Sync Output—Channel D                                                                                          |

| 125                                                                                                          | SDIND <sup>1</sup>                                | I     | Serial Data Input—Channel D                                                                                                      |

| 126                                                                                                          | SDFID                                             | I     | Serial Data Frame Input—Channel D                                                                                                |

REV. A -12-

NOTES  $^{1}Pins$  with a Pull-Down resistor of nominal 70 k $\Omega.$   $^{2}Pins$  with a Pull-Up resistor of nominal 70 k $\Omega.$

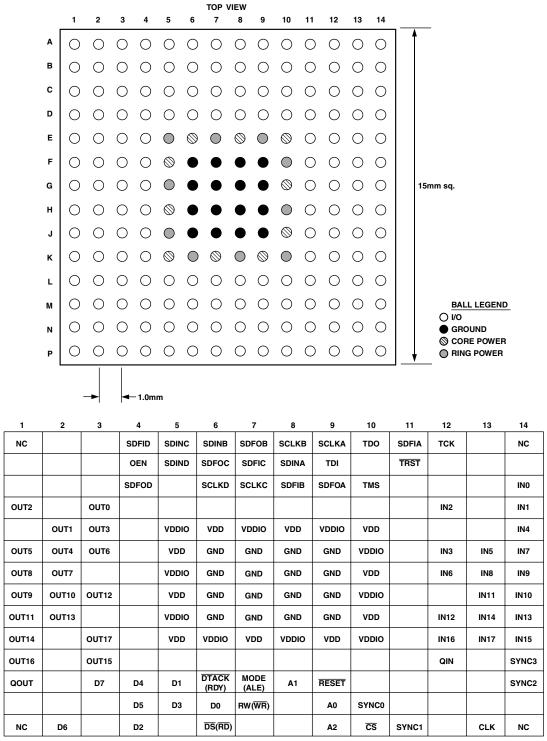

#### PIN CONFIGURATION 196-Lead CSPBGA

NC = NO CONNECT

Α

В

С

D

Е

F

G

Н

κ

L

М

N

REV. A -13-

### 196-LEAD FUNCTION DESCRIPTIONS

| Mnemonic                                                  | Type  | Function                                                |

|-----------------------------------------------------------|-------|---------------------------------------------------------|

| POWER SUPPLY                                              |       |                                                         |

| VDD                                                       | P     | 2.5 V Supply                                            |

| VDDIO                                                     | P     | 3.3 V IO Supply                                         |

| GND                                                       | G     | Ground                                                  |

| INPUTS                                                    |       |                                                         |

| INOUT[17:0] <sup>1</sup>                                  | I/O   | A Input Data (Mantissa)                                 |

| QIN <sup>1</sup>                                          | I     | When HIGH Indicates Q Input Data (Complex Input Mode)   |

| RESET <sup>2</sup>                                        | Ī     | Active LOW Reset Pin                                    |

| CLK <sup>1</sup>                                          | Ī     | Input Clock                                             |

| SYNC0 <sup>1</sup>                                        | Ī     | All Sync Pins Go to All Four Output Channels            |

| SYNC1 <sup>1</sup>                                        | Ī     | All Sync Pins Go to All Four Output Channels            |

| SYNC2 <sup>1</sup>                                        | Ī     | All Sync Pins Go to All Four Output Channels            |

| SYNC3 <sup>1</sup>                                        | I     | All Sync Pins Go to All Four Output Channels            |

| SDINA <sup>1</sup>                                        | Ī     | Serial Data Input—Channel A                             |

| SDINB <sup>1</sup>                                        | Ī     | Serial Data Input—Channel B                             |

| SDINC <sup>1</sup>                                        | Ī     | Serial Data Input—Channel C                             |

| SDINC SDIND <sup>1</sup>                                  | I     | Serial Data Input—Channel D                             |

| <u>CS</u>                                                 | I     | Active LOW Chip Select                                  |

| CONTROL                                                   | 1     | Netive Bo w omp better                                  |

| SCLKA                                                     | I/O   | Bidirectional Serial Clock—Channel A                    |

| SCLKA<br>SCLKB                                            | I/O   | Bidirectional Serial Clock—Channel B                    |

| SCLKG                                                     | I/O   | Bidirectional Serial Clock—Channel C                    |

|                                                           | I/O   |                                                         |

| SCLKD                                                     |       | Bidirectional Serial Clock—Channel D                    |

| SDFOA                                                     | 0     | Serial Data Frame Sync Output—Channel A                 |

| SDFOB                                                     | 0     | Serial Data Frame Sync Output—Channel B                 |

| SDFOC                                                     | -     | Serial Data Frame Sync Output—Channel C                 |

| SDFOD                                                     | O     | Serial Data Frame Sync Output—Channel D                 |

| SDFIA                                                     | I     | Serial Data Frame Input—Channel A                       |

| SDFIB                                                     | I     | Serial Data Frame Input—Channel B                       |

| SDFIC                                                     |       | Serial Data Frame Input—Channel C                       |

| SDFID<br>OEN <sup>1</sup>                                 | I     | Serial Data Frame Input—Channel D                       |

| MICROPORT CONTROL                                         | I     | Active High Output Enable Pin                           |

|                                                           |       | Division D                                              |

| D[7:0]                                                    | I/O/T | Bidirectional Microport Data                            |

| A[2:0]                                                    | I     | Microport Address Bus                                   |

| DS (RD)                                                   | I O/T | Active Low Data Strobe (Active Low Read)                |

| DTACK (RDY) <sup>2</sup>                                  | O/T   | Active Low Data Acknowledge (Microport Status Bit)      |

| $RW(\overline{WR})$                                       | I     | Read Write (Active Low Write)                           |

| MODE                                                      | I     | Intel or Motorola Mode Select                           |

| OUTPUTS                                                   | T     |                                                         |

| OUT[17:0]                                                 | 0     | Wideband Output Data                                    |

| QOUT                                                      | 0     | When HIGH Indicates Q Output Data (Complex Output Mode) |

| TAG AND BIST                                              | 1     |                                                         |

| $\overline{\Gamma}\overline{R}\overline{S}\overline{T}^2$ | I     | Test Reset Pin (Active Low)                             |

| $\Gamma CK^1$                                             | I     | Test Clock Input                                        |

| $TMS^2$                                                   | I     | Test Mode Select Input                                  |

| TDO                                                       | O/T   | Test Data Output                                        |

| $\mathrm{TDI}^1$                                          | I     | Test Data Input                                         |

REV. A -14-

<sup>&</sup>lt;sup>1</sup>Pins with a Pull-Down resistor of nominal 70 kΩ. <sup>2</sup>Pins with a Pull-Up resistors of nominal 70 kΩ.

#### CONTROL REGISTER ADDRESS NOTATION

Register address notation and bit assignment referred to throughout this data sheet are as follows: There are eight, one-digit "External" register addresses in decimal format. "Internal" address notation (read from left to right) begins with "0x", meaning the address that follows is hexadecimal. The next three characters represent the address. The first number or character is the MSB of the address. If an "n" is present, its value can be 1, 2, 3, or 4 and it depends upon the channel that is being addressed (A, B, C, or D). The remaining two digits preceding the colon (if present) are the LSBs of the address. If a colon follows the address, then the succeeding digits tell the user what bit number(s) is/are involved in decimal format. For example, 0xn24:7-0.

#### **SERIAL DATA PORT**

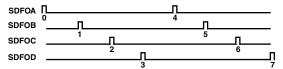

The AD6623 has four independent Serial Ports (A, B, C, and D), and each accepts data to its own channel (A, B, C, or D) of the device. Each Serial Port has four pins: SCLK (Serial CLocK), SDFO (Serial Data Frame Out), SDFI (Serial Data Frame In), and SDIN (Serial Data INput). SDFI and SDIN are inputs, SDFO is an output, and SCLK is either input or output depending on the state of SCS (Serial Clock Slave: 0xn16, Bit 4). Each channel can be operated either as a Master or Slave channel depending upon SCS. The Serial Port can be self-framing or accept external framing from the SFDI pin or from the previous adjacent channel (0xn16, Bits 7 and 6).

#### Serial Master Mode (SCS = 0)

In master mode, SCLK is created by a programmable internal counter that divides CLK. When the channel is "sleeping," SCLK is held low. SCLK becomes active on the first rising edge of CLK after Channel sleep is removed (D0 through D3 of external address 4). Once active, the SCLK frequency is determined by the CLK frequency and the SCLK divider, according to the equations below.

AD6623 mode:

$$f_{SCLK} = \frac{f_{CLK}}{SCLK divider + 1} \tag{1}$$

AD6622 mode:

$$f_{SCLK} = \frac{f_{CLK}}{2 \times (SCLKdivider + 1)}$$

(2)

The SCLK divider is a 5-bit unsigned value located at Internal Channel Address 0xn0D (Bits 4–0), where "n" is 1, 2, 3, or 4 for the chosen channel A, B, C, or D, respectively. The user must select the SCLK divider to insure that SCLK is fast enough to accept full input sample words at the input sample rate. See the design example at the end of this section. The maximum SCLK frequency is equal to the CLK when operating in AD6623 mode serial clock master. When operating in AD6622 compatible mode, the maximum SCLK frequency is one-half the CLK. The minimum SCLK frequency is 1/32 of the CLK frequency in AD6623 mode or 1/64 of the CLK frequency when in AD6622 mode. SDFO changes on the positive edge of SCLK when in master mode. SDIN is captured on positive edge when SCLK is in master mode.

#### Serial Slave Mode (SCS = 1)

Any of the AD6623 serial ports may be operated in the serial slave mode. In this mode, the selected AD6623 channel requires that an external device such as a DSP to supply the SCLK. This is done to synchronize the serial port to meet an external timing requirement. SDIN is captured on negative edge of SCLK when in slave mode.

#### **Serial Data Framing**

The SDIN input pin of each transmit channel of the AD6623 receives data from an external DSP to be digitally filtered, interpolated, and then modulated by the NCO-generated carrier. Serial data from the DSP to the AD6623 is sent as a series of blocks or frames. The length of each block is a function of the desired output format that is supported by the AD6623. Block length may range from 1 bit (MSK) to 32 bits of I and Q data.

The flow of data to the SDIN input is regulated either by the AD6623 (in Self-Framing Mode) or by the external DSP (using AD6623 External Framing Mode). This is accomplished by generating a pulse, SDFO or SDFI, to indicate that the next frame or serial data block is ready to be input or sent to the AD6623. Functions of the two pins, SDFO and SDFI, are fully described in the framing modes that follow.

#### **Self-Framing Mode**

In this mode Bit 7 of register 0xn16 is set low. The serial data frame output, SDFO, generates a self-framing data request and is pulsed high for one SCLK cycle at the input sample rate. In this mode, the SDFI pin is not used, and the SDFO signal would be programmed to be a serial data frame request (0xn16, Bit 5 = 0). SDFO is used to provide a sync signal to the host. The input sample rate is determined by the CLK divided by channel interpolation factor. If the SCLK rate is not an integer multiple of the input sample rate, then the SDFO will continually adjust the period by one SCLK cycle to keep the average SDFO rate equal to the input sample rate. When the channel is in sleep mode, SDFO is held low. The first SDFO is delayed by the channel reset latency after the Channel Reset is removed. The channel reset latency varies dependent on channel configuration.

#### **External Framing Mode**

In this mode Bit 7 of register 0xn16 is set high. The external framing can come from either the SDFI pin (0xn16, Bit 6 = 0) or the previous adjacent channel (0xn16, Bit 6 = 1). In the case of external framing from a previous channel, it uses the internal frame end signal for serial data frame synchronizing. When in master mode, SDFO and SDFI transition on the positive edge of SCLK, and SDIN is captured on the positive edge of SCLK. When in slave mode, SDFO and SDFI transition on the negative edge of SCLK, and SDIN is captured on the negative edge of SCLK.

#### **Serial Port Cascade Configuration**

In this case the SDFO signal from the last channel of the first chip would be programmed to be a serial data frame end (SFE: $0 \times 16$ , Bit 5 = 1). This SDFO signal would then be fed as an input for the second cascaded chip's SDFI pin input. The second chip would be programmed to accept external framing from the SDFI pin ( $0 \times 16$ , Bit 7 = 1, Bit 6 = 0).

REV. A –15–

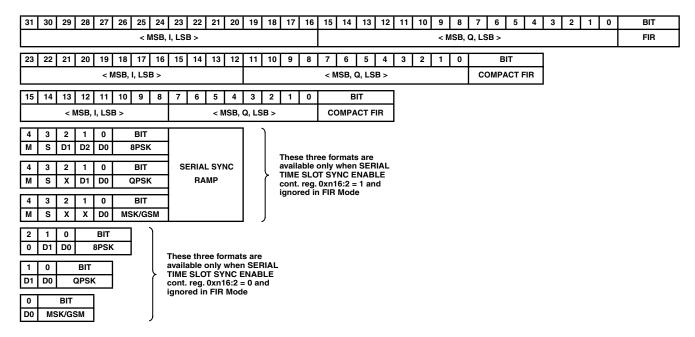

#### **Serial Data Format**

The format of data applied to the serial port is determined by the RCF mode selected in Control Register 0xn0C. Below is a table showing the RCF modes and input data format that it sets.

Table I. Serial Data Format

| 0xn0C<br>Bit 6 | 0xn0C<br>Bit 5 | 0xn0C<br>Bit 4 | Serial Data<br>Word Length | RCF<br>Mode    |

|----------------|----------------|----------------|----------------------------|----------------|

| 0              | 0              | 0              | 32                         | FIR            |

| 0              | 0              | 1              |                            | $\pi/4$ -DQPSK |

| 0              | 1              | 0              |                            | GMSK           |

| 0              | 1              | 1              |                            | MSK            |

| 1              | 0              | 0              | 24 (Bit 9 is high)         | FIR,           |

|                |                |                | 16 (Bit 9 is low)          | compact        |

| 1              | 0              | 1              |                            | 8-PSK          |

| 1              | 1              | 0              |                            | $3\pi/8-8-PSK$ |

| 1              | 1              | 1              |                            | QPSK           |

The serial data input, SDIN, accepts 32-bit words as channel input data. The 32-bit word is interpreted as two 16-bit two's complement quadrature words, I followed by Q, MSB first. This results in linear I and Q data being provided to the RCF. The first bit is shifted into the serial port starting on the next rising edge of SCLK after the SDFO pulse. Figure 16 shows a timing diagram for SCLK master (SCS = 0) and SDFO set for frame request (SFE = 0).

Figure 16. Serial Port Switching Characteristics

As an example of the Serial Port operation, consider a CLK frequency of 62.208 MHz and a channel interpolation of 2560. In that case, the input sample rate is 24.3 kSPS (62.208 MHz/2560), which is also the SDFO rate. Substituting,  $f_{SCLK} \ge 32$  3  $f_{SDFO}$  into the equation and solving for SCLKdivider, we find the minimum value for SCLKdivider according to the equation below.

$$SCLKdivider \le \frac{f_{CLK}}{32 \times f_{SDFO}}$$

(3)

Evaluating this equation for our example, SCLKdivider must be less than or equal to 79. Since the SCLKdivider channel register is a 5-bit unsigned number it can only range from 0 to 31. Any value in that range will be valid for this example, but if it is important that the SDFO period is constant, then there is another restriction. For regular frames, the ratio  $f_{\text{SCLK}}/f_{\text{SDFO}}$  must be equal to an integer of 32 or larger. For this example, constant SDFO periods can only be achieved with an SCLK divider of 31 or less.

See Table II for usable SCLK divider values and the corresponding SCLK and  $f_{SCLK}/f_{SDFO}$  ratio for the example of L = 2560.

In conclusion, SDFO rate is determined by the AD6623 CLK rate and the interpolation rate of the channel. The SDFO rate is equal to the channel input rate. The channel interpolation is equal to RCF interpolation times CIC5 interpolation, times CIC2 interpolation:

$$\left(L = L_{RCF} \times L_{CIC5} \times \frac{L_{CRIC2}}{M_{CRIC2}}\right)$$

(4)

The SCLK divide ratio is determined by SCLKdivider as shown in equation 3. The SCLK must be fast enough to input 32 bits of data prior to the next SDFO. Extra SCLKs are ignored by the serial port.

Table II. Example of Usable SCLK Divider Values and  $f_{SCLK}/f_{SDFO}$  Ratios for L = 2560