## General Description

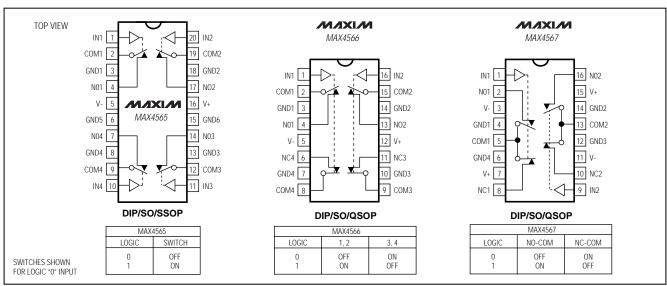

The MAX4565/MAX4566/MAX4567 are low-voltage T-switches designed for switching RF and video signals from DC to 350MHz in  $50\Omega$  and  $75\Omega$  systems. The MAX4565 contains four normally open single-pole/singlethrow (SPST) switches. The MAX4566 contains two dual SPST switches (one normally open, one normally closed.) The MAX4567 contains two single-pole/double-throw (SPDT) switches.

Each switch is constructed in a "T" configuration, ensuring excellent high-frequency off isolation and crosstalk of -83dB at 10MHz. They can handle Rail-to-Rail® analog signals in either direction. On-resistance ( $60\Omega$  max) is matched between switches to  $2.5\Omega$  max and is flat ( $2\Omega$ max) over the specified signal range, using ±5V supplies. The off leakage current is less than 5nA at +25°C and 50nA at +85°C.

These CMOS switches can operate with dual power supplies ranging from  $\pm 2.7V$  to  $\pm 6V$  or a single supply between +2.7V and +12V. All digital inputs have 0.8V/2.4V logic thresholds, ensuring both TTL- and CMOS-logic compatibility when using  $\pm 5V$  or a single +5V supply.

#### **Applications**

RF Switching

Video Signal Routing

High-Speed Data Acquisition

Test Equipment

ATE Equipment

Networking

# **Features**

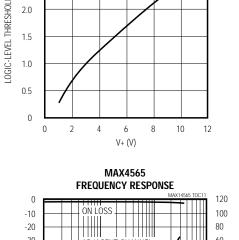

- ♦ High 50Ω Off Isolation: -83dB at 10MHz

- ♦ Low 50Ω Crosstalk: -87dB at 10MHz

- ♦ DC to 350MHz -3dB Signal Bandwidth

- ♦ 60Ω Signal Paths with ±5V Supplies

- **♦ 2.5**Ω Signal-Path Matching with ±5V Supplies

- ♦ 2Ω Signal-Path Flatness with ±5V Supplies

- ♦ Low 50Ω Insertion Loss: 2.5dB at 100MHz

- ♦ ±2.7V to ±6V Dual Supplies +2.7V to +12V Single Supply

- ♦ Low Power Consumption: <1μW

- ♦ Rail-to-Rail Bidirectional Signal Handling

- ♦ Pin Compatible with Industry-Standard DG540, DG542, DG643

- → >2kV ESD Protection per Method 3015.7

- **♦ TTL/CMOS-Compatible Inputs** with Single +5V or ±5V

## **Ordering Information**

| PART       | TEMP. RANGE  | PIN-PACKAGE    |

|------------|--------------|----------------|

| MAX4565CPP | 0°C to +70°C | 20 Plastic DIP |

| MAX4565CWP | 0°C to +70°C | 20 Wide SO     |

Ordering Information continued at end of data sheet.

# Pin Configurations/Functional Diagrams/Truth Tables

Rail-to-Rail is a registered trademark of Nippon Motorola Ltd.

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V+0.3V, +13.0V                                                 |

|----------------------------------------------------------------|

| V13.0V, +0.3V                                                  |

| V+ to V0.3V, +13.0V                                            |

| All Other Pins (Note 1)(V 0.3V) to (V+ + 0.3V)                 |

| Continuous Current into Any Terminal±25mA                      |

| Peak Current into Any Terminal                                 |

| (pulsed at 1ms, 10% duty cycle)±50mA                           |

| ESD per Method 3015.7>2000\                                    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) (Note 2) |

| 16-Pin Plastic DIP                                             |

| (derate 10.53mW/°C above +70°C)842mW                           |

| 16-Pin Narrow SO                                      |

|-------------------------------------------------------|

| (derate 8.70mW/°C above +70°C)696mW                   |

| 16-Pin QSOP (derate 8.3mW/°C above +70°C) 667mW       |

| 20-Pin Plastic DIP (derate 8.0mW/°C above +70°C)640mW |

| 20-Pin Wide SO (derate 10.00mW/°C above +70°C) 800mW  |

| 20-Pin SSOP (derate 8.0mW/°C above +70°C) 640mW       |

| Operating Temperature Ranges                          |

| MAX456_C_ E0°C to +70°C                               |

| MAX456_E_ E40°C to +85°C                              |

| Storage Temperature Range65°C to +150°C               |

| Lead Temperature (soldering, 10sec)+300°C             |

**Note 1:** Voltages on all other pins exceeding V+ or V- are clamped by internal diodes. Limit forward diode current to maximum current rating.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS—Dual Supplies**

$(V+=+4.5V \text{ to } +5.5V, V-=-4.5V \text{ to } -5.5V, V_{INL}=0.8V, V_{INH}=2.4V, V_{GND}=0V, T_A=T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A=+25^{\circ}C.)$

| PARAMETER                                      | SYMBOL                                 | CONDITIONS                                                                    | TA    | MIN  | TYP<br>(Note 2) | MAX  | UNITS |

|------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------|-------|------|-----------------|------|-------|

| ANALOG SWITCH                                  |                                        |                                                                               |       |      |                 |      |       |

| Analog Signal Range                            | V <sub>COM_</sub> ,                    | (Note 3)                                                                      | C, E  | V-   |                 | V+   | V     |

| Signal Dath On Desistance                      | D                                      | V+ = 4.5V, V- = -4.5V,                                                        | +25°C |      | 46              | 60   | Ω     |

| Signal-Path On-Resistance                      | R <sub>ON</sub>                        | $V_{COM} = \pm 2V$ , $I_{COM} = 10mA$                                         | C, E  |      |                 | 80   |       |

| Signal-Path On-Resistance Match                | ADou                                   | V+ = 4.5V, V- = -4.5V,                                                        | +25°C |      | 1               | 2.5  | 5 Ω   |

| Between Channels (Note 4)                      | ΔRON                                   | $V_{COM} = \pm 2V$ , $I_{COM} = 10$ mA                                        | C, E  | C, E | 3               | _ 52 |       |

| Signal-Path On-Resistance<br>Flatness (Note 5) | RFLAT(ON)                              | V+ = 5V; V- = -5V; V <sub>COM</sub> = 1V,<br>0V, -1V; I <sub>COM</sub> = 10mA | +25°C |      | 0.3             | 2    | Ω     |

| NO_, NC_ Off Leakage Current                   | INO (OFF),                             | V+ = 5.5V, V- = -5.5V,                                                        | +25°C | -1   | 0.02            | 1    |       |

| (Note 6)                                       | INC_(OFF)                              | $V_{COM} = \pm 4.5V, V_{N} = \mp 4.5V$                                        | C, E  | -10  |                 | 10   | nA    |

| COM_ Off Leakage Current                       | loon (off)                             | V+ = 5.5V, V- = -5.5V,                                                        | +25°C | -1   | 0.02            | 1    |       |

| (Note 6)                                       | ICOM_(OFF)                             | $V_{COM} = \pm 4.5V, V_{N} = \mp 4.5V$                                        | C, E  | -10  |                 | 10   | nA    |

| COM_ On Leakage Current                        | loor (or)                              | V+ = 5.5V, V- = -5.5V,                                                        | +25°C | -2   | 0.04            | 2    | nA    |

| (Note 6)                                       | ICOM_(ON)                              | $V_{COM} = \pm 4.5V$                                                          | C, E  | -20  |                 | 20   | 1 IIA |

| LOGIC INPUT                                    |                                        |                                                                               |       |      |                 |      | •     |

| IN_ Input Logic Threshold High                 | V <sub>IN_</sub> H                     |                                                                               | C, E  |      | 1.5             | 2.4  | V     |

| IN_ Input Logic Threshold Low                  | V <sub>IN_L</sub>                      |                                                                               | C, E  | 0.8  | 1.5             |      | V     |

| IN_ Input Current Logic High or Low            | I <sub>INH</sub> _, I <sub>INL</sub> _ | V <sub>IN</sub> _ = 0.8V or 2.4V                                              | C, E  | -1   | 0.03            | 1    | μА    |

## **ELECTRICAL CHARACTERISTICS—Dual Supplies (continued)**

$(V+=+4.5V \text{ to } +5.5V, V-=-4.5V \text{ to } -5.5V, V_{INL}=0.8V, V_{INH}=2.4V, V_{GND}=0V, T_A=T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A=+25^{\circ}C$ .)

| PARAMETER                                           | SYMBOL               | CONDITIONS                                              |                       | TA    | MIN | TYP<br>(Note 2) | MAX | UNITS |  |

|-----------------------------------------------------|----------------------|---------------------------------------------------------|-----------------------|-------|-----|-----------------|-----|-------|--|

| SWITCH DYNAMIC CHARACTER                            | RISTICS              |                                                         |                       |       |     |                 |     | 1     |  |

| Turn-On Time                                        | tou                  | V <sub>COM</sub> _ = ±3V, V+ =                          | 5V, V- = -5V,         | +25°C |     | 75              | 150 | nc    |  |

| Turr-On Time                                        | ton                  | Figure 3                                                |                       | C, E  |     |                 | 200 | ns    |  |

| Turn-Off Time                                       | torr                 | V <sub>COM</sub> = ±3V, V+ =                            | 5V, V- = -5V,         | +25°C |     | 30              | 100 | ns    |  |

| Turn-On Time                                        | toff                 | Figure 3                                                |                       | C, E  |     |                 | 120 | 1 115 |  |

| Break-Before-Make Time Delay (MAX4566/MAX4567 only) | t <sub>BBM</sub>     | $V_{COM} = \pm 3V, V + =$ Figure 4                      | 5V, V- = -5V,         | +25°C | 5   | 30              |     | ns    |  |

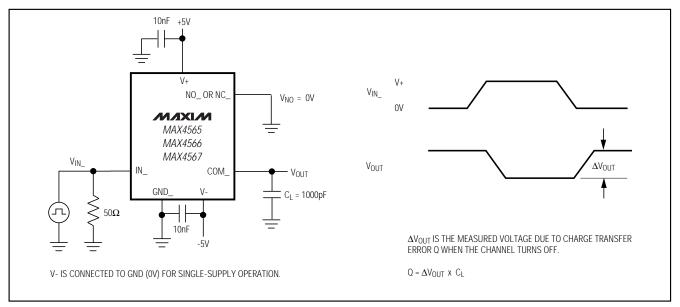

| Charge Injection (Note 3)                           | Q                    | C <sub>L</sub> = 1.0nF, V <sub>NO</sub> = 0<br>Figure 5 | OV, $R_S = 0\Omega$ , | +25°C |     | 25              | 60  | рС    |  |

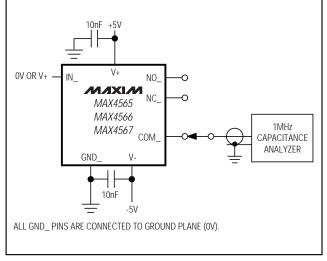

| NO_, NC_ Off Capacitance                            | C <sub>N_(OFF)</sub> | V <sub>NO_</sub> = GND, f = 1M                          | Hz, Figure 7          | +25°C |     | 2.5             |     | pF    |  |

| COM_ Off Capacitance                                | CCOM_(OFF)           | V <sub>COM</sub> _ = 0V,<br>f = 1MHz,<br>Figure 7       | MAX4565,<br>MAX4566   | +25°C |     | 2.5             |     | pF    |  |

|                                                     |                      | ., ., .,                                                | MAX4565               | +25°C | 6   |                 |     |       |  |

| COM_ On Capacitance                                 | CCOM_(ON)            | $V_{COM} = V_{NO} = 0V,$<br>f = 1MHz, Figure 7          | MAX4566               |       |     | 6               |     | рF    |  |

|                                                     |                      | T = TWITZ, Tigute 7                                     | MAX4567               |       |     | 7               |     |       |  |

|                                                     |                      | $R_L = 50\Omega$ ,                                      | MAX4565               |       | -83 |                 |     |       |  |

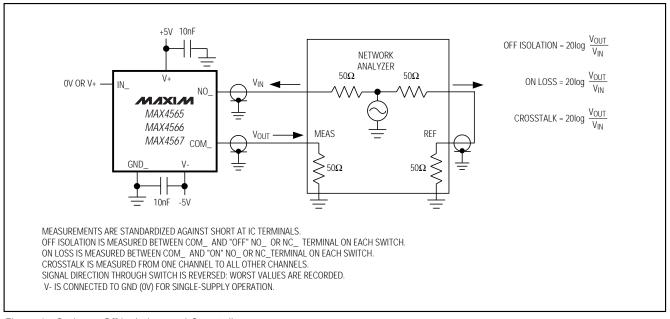

| Off Isolation (Note 7)                              | V <sub>ISO</sub>     | $V_{COM} = 1V_{RMS}$                                    | MAX4566               | +25°C |     | -82             |     | dB    |  |

|                                                     |                      | f = 10MHz, Figure 6                                     | MAX4567               |       |     | -83             |     |       |  |

| Channel-to-Channel Crosstalk                        |                      | $R_L = 50\Omega$ , $V_{COM} =$                          | MAX4565               |       |     | -92             |     |       |  |

| (Note 8)                                            | V <sub>CT</sub>      | $1V_{RMS}$ , $f = 10MHz$ ,                              | MAX4566               | +25°C |     | -85             |     | dB    |  |

| (1111 -)                                            |                      | Figure 6                                                | MAX4567               |       |     | -87             |     |       |  |

| -3dB Bandwidth (Note 9)                             | BW                   | Figure 6, $R_L = 50\Omega$                              |                       | +25°C |     | 350             |     | MHz   |  |

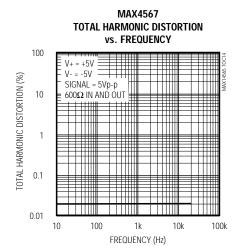

| Distortion                                          | THD+N                | $V_{IN} = 5Vp-p$ , $f < 20kHz$ , $600\Omega$ in and out |                       | +25°C |     | 0.02            |     | %     |  |

| POWER SUPPLY                                        | •                    |                                                         |                       |       |     |                 |     | •     |  |

| Power-Supply Range                                  | V+, V-               |                                                         |                       | C, E  | -6  |                 | +6  | V     |  |

| V+ Supply Current                                   | 1+                   | V+ = 5.5V, all V <sub>IN</sub> _ =                      | 0\/ or \/+            | +25°C | -1  | 0.05            | 1   | μΑ    |  |

| ут зарргу синен                                     | IΤ                   | v i = 3.5 v, all v[N_ =                                 | O V OI V T            | C, E  | -10 |                 | 10  | μΛ    |  |

| V - Supply Current                                  | -                    | V- = -5.5V                                              |                       | +25°C | -1  | 0.05            | 1   | μΑ    |  |

| v - Supply Current                                  | '                    | v-                                                      |                       | C, E  | -10 |                 | 10  |       |  |

## **ELECTRICAL CHARACTERISTICS—Single +5V Supply**

$(V_{+} = +4.5V \text{ to } +5.5V, V_{-} = 0V, V_{INL} = 0.8V, V_{INH} = 2.4V, V_{GND} = 0V, T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_{A} = +25^{\circ}C$ .)

| PARAMETER                                           | SYMBOL                                | CONDITIONS                                                       | TA    | MIN | TYP<br>(Note 2) | MAX | UNITS |

|-----------------------------------------------------|---------------------------------------|------------------------------------------------------------------|-------|-----|-----------------|-----|-------|

| ANALOG SWITCH                                       |                                       |                                                                  |       |     |                 |     |       |

| Analog Signal Range                                 | V <sub>COM_</sub> ,                   | (Note 3)                                                         | +25°C | 0   |                 | V+  | V     |

| Signal-Path On-Resistance                           | Ron                                   | V+ = 4.5V, V <sub>COM</sub> _ = 3.5V,                            | +25°C |     | 68              | 120 | Ω     |

| Signal-Fatti Off-Kesistance                         | KON                                   | I <sub>COM</sub> _ = 1mA                                         | C, E  |     |                 | 150 | 32    |

| Signal-Path On-Resistance                           | ΔRON                                  | $V+ = 4.5V, V_{COM} = 3.5V,$                                     | +25°C |     | 2               | 5   | Ω     |

| Match                                               | ZIVON                                 | I <sub>COM</sub> _ = 1mA                                         | C, E  |     |                 | 6   | 22    |

| NO_, NC_ Off Leakage Current                        | I <sub>NO_(OFF)</sub> ,               | $V+ = 5.5V, V_{COM} = 1V,$                                       | +25°C | -1  |                 | 1   | nA    |

| (Notes 6, 10)                                       | INC_(OFF)                             | $V_{N_{-}} = 4.5V$                                               | C, E  | -10 |                 | 10  | ] "   |

| COM_ Off Leakage Current                            | January (055)                         | $V+ = 5.5V, V_{COM} = 1V,$                                       | +25°C | -1  |                 | 1   | nA    |

| (Notes 6, 10)                                       | ICOM_(OFF)                            | $V_{N_{-}} = 4.5V$                                               | C, E  | -10 |                 | 10  | 0 nA  |

| COM_ On Leakage Current                             | laarr (arr                            | V. 5 5V: V 1V 4 5V                                               | +25°C | -2  |                 | 2   | nA    |

| (Notes 6, 10)                                       | ICOM_(ON)                             | $V + = 5.5V; V_{COM} = 1V, 4.5V$                                 | C, E  | -20 |                 | 20  | 1 11A |

| LOGIC INPUT                                         |                                       |                                                                  |       |     |                 |     |       |

| IN_ Input Logic Threshold High                      | VIN_H                                 |                                                                  | C, E  |     | 1.5             | 2.4 | V     |

| IN_ Input Logic Threshold Low                       | V <sub>IN_L</sub>                     |                                                                  | C, E  | 0.8 | 1.5             |     | V     |

| IN_ Input Current Logic High or Low                 | I <sub>INH_</sub> , I <sub>INL_</sub> | V <sub>IN</sub> _ = 0.8V or 2.4V                                 | C, E  | -1  | 0.001           | 1   | μΑ    |

| SWITCH DYNAMIC CHARACTE                             | RISTICS                               |                                                                  |       |     |                 |     |       |

| T 0 T                                               |                                       | $V_{COM} = 3V, V_{+} = 5V,$                                      | +25°C |     | 130             | 200 | ns    |

| Turn-On Time                                        | ton                                   | Figure 3                                                         | C, E  |     |                 | 250 |       |

| T 0% T'                                             |                                       | V <sub>COM</sub> _ = 3V, V+ = 5V,                                | +25°C |     | 30              | 120 |       |

| Turn-Off Time                                       | toff                                  | Figure 3                                                         | C, E  |     |                 | 150 | ns    |

| Break-Before-Make Time Delay (MAX4566/MAX4567 only) | t <sub>BBM</sub>                      | V <sub>COM</sub> _ = 3V, V+ = 5V,<br>Figure 4                    | +25°C | 10  | 90              |     | ns    |

| Charge Injection                                    | Q                                     | $C_L = 1.0$ nF, $V_{NO} = 2.5$ V, $R_S = 0\Omega$ , Figure 5     | +25°C |     | 7               | 25  | рС    |

| Off-Isolation<br>(Note 7)                           | V <sub>ISO</sub>                      | $R_L = 50\Omega$ , $f = 10MHz$ , $V_{COM} = 1V_{RMS}$ , Figure 6 | +25°C |     | -81             |     | dB    |

| Channel-to-Channel Crosstalk (Note 8)               | Vст                                   | $R_L = 50\Omega$ , $f = 10MHz$ , $V_{COM} = 1V_{RMS}$ , Figure 6 | +25°C |     | -86             |     | dB    |

| -3dB Bandwidth (Note 9)                             | BW                                    | $R_L = 50\Omega$ , Figure 6                                      | +25°C |     | 320             |     | MHz   |

| POWER SUPPLY                                        | 1                                     | 1                                                                | 1     |     |                 |     | -     |

| V. Supply Current                                   | L                                     | V. E.E.V. Oll V. O.V. 25 V.                                      | +25°C | -1  | 0.05            | 1   |       |

| V+ Supply Current                                   | 1+                                    | $V+ = 5.5V$ , all $V_{IN} = 0V$ or $V+$                          | C, E  | -10 |                 | 10  | - μΑ  |

## **ELECTRICAL CHARACTERISTICS—Single +3V Supply**

$(V+=+2.7V \text{ to } +3.6V, V-=0V, V_{INL}=0.8V, V_{INH}=2.4V, V_{GND}=0V, T_A=T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A=+25^{\circ}C.)$

| PARAMETER                                           | SYMBOL                                | CONDITIONS                                                             | TA    | MIN | TYP<br>(Note 2) | MAX | UNITS      |  |  |  |

|-----------------------------------------------------|---------------------------------------|------------------------------------------------------------------------|-------|-----|-----------------|-----|------------|--|--|--|

| ANALOG SWITCH                                       |                                       |                                                                        |       |     |                 |     |            |  |  |  |

| Analog Signal Range                                 | V <sub>COM_</sub> ,                   | (Note 3)                                                               | +25°C | 0   |                 | V+  | V          |  |  |  |

| Signal-Path On-Resistance                           | Ron                                   | V+ = 2.7V, V <sub>COM</sub> _ = 1V,                                    | +25°C |     | 150             | 350 | Ω          |  |  |  |

| Signal Fath Of Resistance                           | NON                                   | I <sub>COM</sub> _ = 1mA                                               | C, E  |     |                 | 450 | 32         |  |  |  |

| LOGIC INPUT                                         |                                       |                                                                        |       |     |                 |     |            |  |  |  |

| IN_ Input Logic Threshold High                      | V <sub>IN</sub> _H                    | (Note 3)                                                               | C, E  |     | 1.0             | 2.4 | V          |  |  |  |

| IN_ Input Logic Threshold Low                       | V <sub>IN_L</sub>                     | (Note 3)                                                               | C, E  | 0.8 | 1.0             |     | V          |  |  |  |

| IN_ Input Current Logic High or Low                 | I <sub>INH_</sub> , I <sub>INL_</sub> | V <sub>IN</sub> _ = 0.8V or 2.4V (Note 3)                              | C, E  | -1  |                 | 1   | μA         |  |  |  |

| SWITCH DYNAMIC CHARACTER                            | RISTICS (Note                         | 3)                                                                     |       |     |                 |     | - <b>!</b> |  |  |  |

| Turn-On Time                                        | +                                     | V <sub>COM</sub> _ = 1.5V, V <sub>+</sub> = 2.7V,<br>Figure 3 (Note 3) | +25°C |     | 270             | 500 | ns         |  |  |  |

| Turn-On Time<br>                                    | ton                                   |                                                                        | C, E  |     |                 | 600 |            |  |  |  |

| Turn-Off Time                                       | +                                     | $V_{COM} = 1.5V, V_{+} = 2.7V,$                                        | +25°C |     | 40              | 100 | nc         |  |  |  |

| Turr-On Time                                        | toff                                  | Figure 3 (Note 3)                                                      | C, E  |     |                 | 120 | - ns       |  |  |  |

| Break-Before-Make Time Delay (MAX4566/MAX4567 only) | t <sub>BBM</sub>                      | V <sub>COM</sub> _ = 1.5V, V+ = 2.7V,<br>Figure 4 (Note 3)             | +25°C | 10  | 120             |     | ns         |  |  |  |

| POWER SUPPLY                                        | 1                                     |                                                                        | 1     |     |                 |     | .1         |  |  |  |

| V. Supply Current                                   | 1+                                    | V 2 6V 2H VIII - OV 25 V :                                             | +25°C | -1  | 0.05            | 1   |            |  |  |  |

| V+ Supply Current                                   | 1+                                    | $V+ = 3.6V$ , all $V_{IN} = 0V$ or $V+$                                | C, E  | -10 |                 | 10  | - μΑ       |  |  |  |

- Note 2: The algebraic convention is used in this data sheet; the most negative value is shown in the minimum column.

- Note 3: Guaranteed by design.

- **Note 4:**  $\Delta R_{ON} = \Delta R_{ON}(MAX) \Delta R_{ON}(MIN)$ .

- **Note 5:** Resistance flatness is defined as the difference between the maximum and the minimum value of on-resistance as measured over the specified analog signal range.

- Note 6: Leakage parameters are 100% tested at the maximum rated hot temperature and guaranteed by correlation at +25°C.

- Note 7: Off isolation =  $20log_{10}$  [V<sub>COM</sub> / (V<sub>NC</sub> or V<sub>NO</sub>)], V<sub>COM</sub> = output, V<sub>NC</sub> or V<sub>NO</sub> = input to off switch.

- Note 8: Between any two switches.

- Note 9: -3dB bandwidth is measured relative to 100kHz.

- Note 10: Leakage testing for single-supply operation is guaranteed by testing with dual supplies.

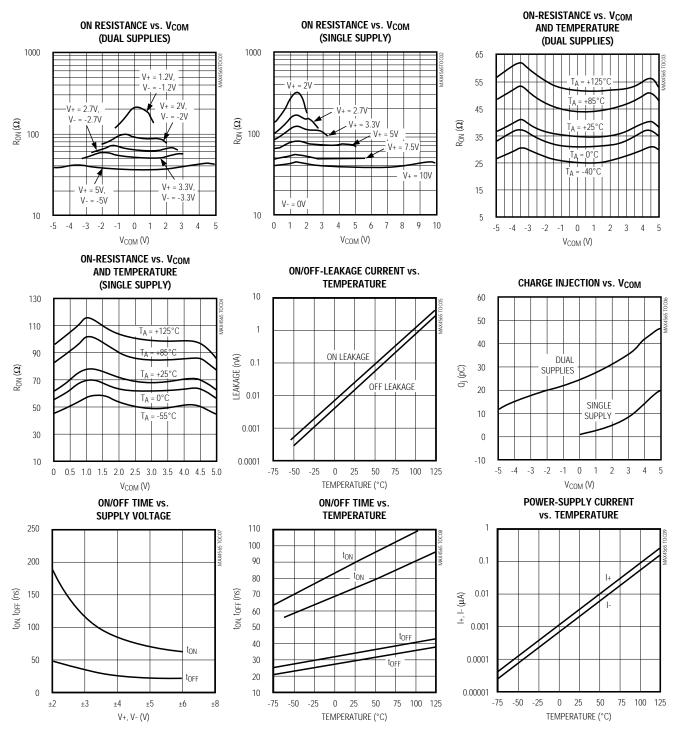

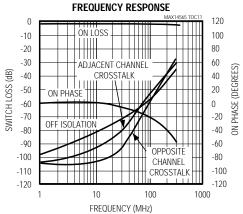

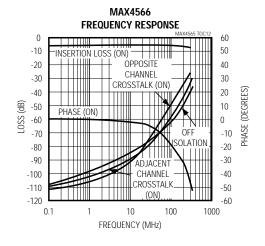

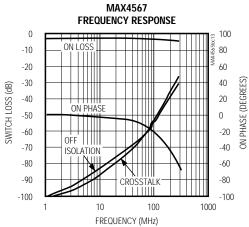

# Typical Operating Characteristics

$(V + = +5V, V - = -5V, T_A = +25$ °C, GND = 0V, packages are surface mount, unless otherwise noted.)

# Typical Operating Characteristics (continued)

$(V + = +5V, V - = -5V, T_A = +25^{\circ}C, GND = 0V, packages are surface mount, unless otherwise noted.)$

#### Pin Description

|                        | PIN          |              | NAME   | FUNCTION*                                                                                                                                              |  |

|------------------------|--------------|--------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX4565                | MAX4566      | MAX4567      | NAIVIE | FUNCTION                                                                                                                                               |  |

| 1, 10, 11,<br>20       | 1, 16        | 1, 9         | IN_    | Digital Control Input                                                                                                                                  |  |

| 3, 6, 8, 13,<br>15, 18 | 3, 7, 10, 14 | 4, 6, 12, 14 | GND_   | RF and Logic Ground. Grounds are not internally connected to each other, and should all be connected to a ground plane (see <i>Grounding</i> section). |  |

| 16                     | 12           | 7, 15        | V+     | Positive Supply-Voltage Input (analog and digital)                                                                                                     |  |

| 5                      | 5            | 3, 11        | V-     | Negative Supply-Voltage Input. Connect to ground plane for single-supply operation.                                                                    |  |

| 4, 7, 14, 17           | 4, 13        | 2, 16        | NO_    | Analog Switch Normally Open** Terminals                                                                                                                |  |

| _                      | 6, 11        | 8, 10        | NC_    | Analog Switch Normally Closed** Terminals                                                                                                              |  |

| 2, 9, 12, 19           | 2, 8, 9, 15  | 5, 13        | COM_   | Analog Switch Common** Terminals                                                                                                                       |  |

- \* All pins have ESD diodes to V- and V+.

- \*\* NO\_ (or NC\_) and COM\_ pins are identical and interchangeable. Either may be considered as an input or output; signals pass equally well in either direction.

## Theory of Operation

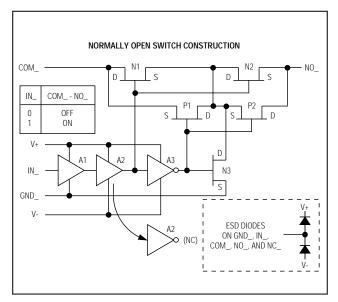

The MAX4565/MAX4566/MAX4567 are high-frequency "T" switches. Each "T" switch consists of two series CMOS switches, with a third N-channel switch at the junction that shunts capacitively-coupled signals to ground when the series switches are off. This produces superior high-frequency signal isolation when the switch is turned off.

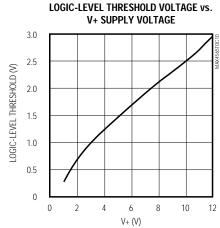

#### Logic-Level Translators

The MAX4565/MAX4566/MAX4567 are constructed as high-frequency "T" switches, as shown in Figure 1. The logic-level input, IN\_, is translated by amplifier A1 into a V+ to V- logic signal that drives amplifier A2. (Amplifier A2 is an inverter for normally closed switches.) Amplifier A2 drives the gates of N-channel MOSFETs N1 and N2 from V+ to V-, turning them fully on or off. The same signal drives inverter A3 (which drives the P-channel MOSFETs P1 and P2) from V+ to V-, turning them fully on or off, and drives the N-channel MOSFET N3 off and on.

The logic-level threshold is determined by V+ and GND\_. The voltage on GND\_ is usually at ground potential, but it may be set to any voltage between (V+ - 2V) and V-. When the voltage between V+ and GND\_ is less than 2V, the level translators become very slow and unreliable. Since individual switches in each package have individual GND\_ pins, they may be set to different voltages. Normally, however, they should all be connected to the ground plane.

Figure 1. T-Switch Construction

#### **Switch On Condition**

When the switch is on, MOSFETs N1, N2, P1, and P2 are on and MOSFET N3 is off. The signal path is COM\_ to NO\_, and because both N-channel and P-channel MOSFETs act as pure resistances, it is symmetrical (i.e., signals may pass in either direction). The off MOSFET, N3, has no DC conduction, but has a small

amount of capacitance to GND\_. The four on MOSFETs also have capacitance to ground that, together with the series resistance, forms a lowpass filter. All of these capacitances are distributed evenly along the series resistance, so they act as a transmission line rather than a simple R-C filter. This helps to explain the exceptional 350MHz bandwidth when the switches are on.

Typical attenuation in  $50\Omega$  systems is -2.5dB and is reasonably flat up to 300MHz. Higher-impedance circuits show even lower attenuation (and vice versa), but slightly lower bandwidth due to the increased effect of the internal and external capacitance and the switch's internal resistance.

The MAX4565/MAX4566/MAX4567 are optimized for  $\pm 5$ V operation. Using lower supply voltages or a single supply increases switching time, increases on-resistance (and therefore on-state attenuation), and increases nonlinearity.

#### **Switch Off Condition**

When the switch is off, MOSFETs N1, N2, P1, and P2 are off and MOSFET N3 is on. The signal path is through the off-capacitances of the series MOSFETs, but it is shunted to ground by N3. This forms a highpass filter whose exact characteristics are dependent on the source and load impedances. In  $50\Omega$  systems, and below 10MHz, the attenuation can exceed 80dB. This value decreases with increasing frequency and increasing circuit impedances. External capacitance and board layout have a major role in determining overall performance.

# Applications Information Power-Supply Considerations

# Overview

The MAX4565/MAX4566/MAX4567 construction is typical of most CMOS analog switches. It has three supply pins: V+, V-, and GND. V+ and V- are used to drive the internal CMOS switches and set the limits of the analog voltage on any switch. Reverse ESD protection diodes are internally connected between each analog signal pin and both V+ and V-. If the voltage on any pin exceeds V+ or V-, one of these diodes will conduct. During normal operation these reverse-biased ESD diodes leak, forming the only current drawn from V-.

Virtually all the analog leakage current is through the ESD diodes. Although the ESD diodes on a given signal pin are identical, and therefore fairly well balanced, they are reverse biased differently. Each is biased by either V+ or V- and the analog signal. This means their

leakages vary as the signal varies. The *difference* in the two diode leakages from the signal path to the V+ and V- pins constitutes the analog signal-path leakage current. All analog leakage current flows to the supply terminals, not to the other switch terminal. This explains how both sides of a given switch can show leakage currents of either the same or opposite polarity.

There is no connection between the analog signal paths and GND. The analog signal paths consist of an N-channel and P-channel MOSFET with their sources and drains paralleled and their gates driven out of phase with V+ and V- by the logic-level translators.

V+ and GND power the internal logic and logic-level translators, and set the input logic thresholds. The logic-level translators convert the logic levels to switched V+ and V- signals to drive the gates of the analog switches. This drive signal is the only connection between the logic supplies and the analog supplies. All pins have ESD protection to V+ and to V-.

Increasing V- has no effect on the logic-level thresholds, but it does increase the drive to the P-channel switches, reducing their on-resistance. V- also sets the negative limit of the analog signal voltage.

The logic-level thresholds are CMOS and TTL compatible when V+ is +5V. As V+ is raised, the threshold increases slightly; when V+ reaches +12V, the level threshold is about 3.1V, which is above the TTL output high-level minimum of 2.8V, but still compatible with CMOS outputs.

#### **Bipolar-Supply Operation**

The MAX4565/MAX4566/MAX4567 operate with bipolar supplies between ±2.7V and ±6V. The V+ and V- supplies need not be symmetrical, but their sum cannot exceed the absolute maximum rating of 13.0V. Do not connect the MAX4565/MAX4566/MAX4567 V+ pin to +3V and connect the logic-level input pins to TTL logic-level signals. TTL logic-level outputs can exceed the absolute maximum ratings, causing damage to the part and/or external circuits.

#### **CAUTION:**

The absolute maximum V+ to V- differential voltage is 13.0V. Typical "±6-Volt" or "12-Volt" supplies with ±10% tolerances can be as high as 13.2V. This voltage can damage the MAX4565/MAX4566/MAX4567. Even ±5% tolerance supplies may have overshoot or noise spikes that exceed 13.0V.

#### Single-Supply Operation

The MAX4565/MAX4566/MAX4567 operate from a single supply between +2.7V and +12V when V- is connected to GND. All of the bipolar precautions must be observed. Note, however, that these parts are optimized for ±5V operation, and most AC and DC characteristics are degraded significantly when departing from ±5V. As the overall supply voltage (V+ to V-) is lowered, switching speed, on-resistance, off isolation, and distortion are degraded. (See *Typical Operating Characteristics*.)

Single-supply operation also limits signal levels and interferes with grounded signals. When V-=0V, AC signals are limited to -0.3V. Voltages below -0.3V can be clipped by the internal ESD-protection diodes, and the parts can be damaged if excessive current flows.

#### Power Off

When power to the MAX4565/MAX4566/MAX4567 is off (i.e., V+=0V and V-=0V), the Absolute Maximum Ratings still apply. This means that neither logic-level inputs on IN\_ nor signals on COM\_, NO\_, or NC\_ can exceed  $\pm 0.3V$ . Voltages beyond  $\pm 0.3V$  cause the internal ESD-protection diodes to conduct, and the parts can be damaged if excessive current flows.

#### Grounding

#### **DC Ground Considerations**

Satisfactory high-frequency operation requires that careful consideration be given to grounding. For most applications, a ground plane is strongly recommended, and all GND\_ pins should be connected to it with solid copper. While the V+ and V- power-supply pins are common to all switches in a given package, each switch has separate ground pins that are not internally connected to each other. This contributes to the overall high-frequency performance and provides added flexibility in some applications, but it can cause problems if it is overlooked. All the GND\_ pins have ESD diodes to V+ and V-.

In systems that have separate digital and analog (signal) grounds, connect these switch GND\_ pins to analog ground. Preserving a good signal ground is much more important than preserving a digital ground.

The logic-level inputs, IN\_, have voltage thresholds determined by V+ and GND\_. (V- does not influence the logic-level threshold.) With +5V and 0V applied to V+ and GND\_, the threshold is about 1.6V, ensuring compatibility with TTL- and CMOS-logic drivers.

The various GND\_ pins can be connected to separate voltage potentials if any or all of the logic-level inputs is

not a normal logic signal. (The GND\_ voltages cannot exceed (V+ - 2V) or V-.) Elevating GND\_ reduces off isolation. For example, using the MAX4565, if GND2–GND6 are connected to 0V and GND1 is connected to V-, then switches 2, 3, and 4 would be TTL/CMOS compatible, but switch 1 (IN1) could be driven with the rail-to-rail output of an op amp operating from V+ and V-. Note, however, that IN\_ can be driven more negative than GND\_, as far as V-. GND\_ does not have to be removed from 0V when IN\_ is driven from bipolar sources, but the voltage on IN\_ should never exceed V-. GND\_ should be separated from 0V only if the logic-level threshold has to be changed.

Any GND\_ pin not connected to 0V should be bypassed to the ground plane with a surface-mount 10nF capacitor to maintain good RF grounding. DC current in the IN\_ and GND\_ pins is less than 1nA, but increases with switching frequency.

On the MAX4565 only, two extra ground pins—GND5 and GND6—are provided to improve isolation and crosstalk. They are not connected to the logic-level circuit. These pins should always be connected to the ground plane with solid copper.

frequency operation. (Prototyping using hand wiring or wire-wrap boards is strongly discouraged.) Connect all OV GND\_ pins to the ground plane with solid copper. (The GND\_ pins extend the high-frequency ground through the package wire-frame, into the silicon itself, thus improving isolation.) The ground plane should be

A ground plane is mandatory for satisfactory high-

AC Ground and Bypassing

solid metal underneath the device, without interruptions. There should be no traces under the device itself. For DIP packages, this applies to both sides of a two-sided board. Failure to observe this will have a minimal effect on the "on" characteristics of the switch at high frequencies, but it will degrade the off isolation and crosstalk.

Bypass all V+ and V- pins to the ground plane with surface-mount 10nF capacitors. For DIP packages, mount the capacitors as close as possible to the pins on the same side of the board as the device. Do not use feedthroughs or vias for bypass capacitors.

For surface-mount packages, bypass capacitors should be mounted on the opposite side of the board from the device. In this case, use short feedthroughs or vias, directly under the V+ and V- pins. Any GND\_ pin not connected to 0V should be similarly bypassed. If V- is 0V, connect it directly to the ground plane with solid copper. Keep all leads short.

The MAX4567 has two V+ and two V- pins. Make DC connections to only one of each to minimize crosstalk. Do not route DC current into one of the V+ or V- pins and out the other V+ or V- pin to other devices. The second set of V+ and V- pins is for AC bypassing only.

For dual-supply operation, the MAX4567 should have four 10nF bypass capacitors connected to each V+ and V- pin as close to the package as possible. For single-supply operation, the MAX4567 should have two 10nF bypass capacitors connected (one to each V+ pin) as close to the package as possible.

On the MAX4565, GND5 and GND6 should always be connected to the ground plane with solid copper to improve isolation and crosstalk.

#### Signal Routing

Keep all signal leads as short as possible. Separate all signal leads from each other and other traces with the ground plane on both sides of the board. Where possible, use coaxial cable instead of printed circuit board traces.

#### **Board Layout**

IC sockets degrade high-frequency performance and should not be used if signal bandwidth exceeds 5MHz. Surface-mount parts, having shorter internal lead frames, provide the best high-frequency performance. Keep all bypass capacitors close to the device, and separate all signal leads with ground planes. Such grounds tend to be wedge-shaped as they get closer to the device. Use vias to connect the ground planes on each side of the board, and place the vias in the apex of the wedge-shaped grounds that separate signal leads. Logic-level signal lead placement is not critical.

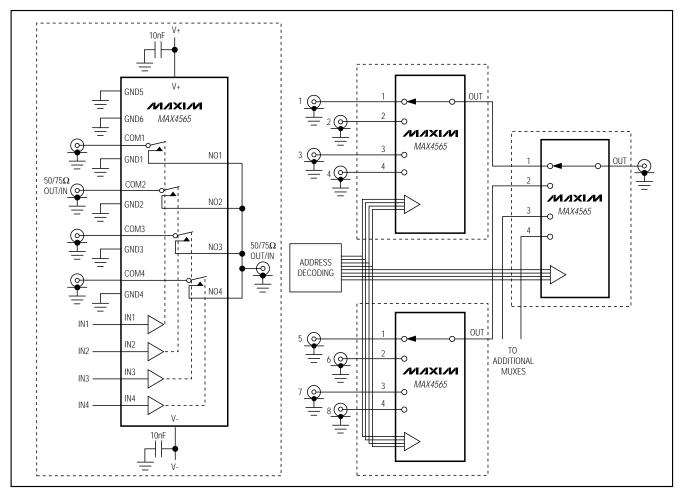

Figure 2. 4-Channel Multiplexer

#### Multiplexer

With its excellent off isolation, the MAX4565 is ideal for use in high-frequency video multiplexers. Figure 2 shows such an application for switching any one of four video inputs to a single output. The same circuit may be used as a demultiplexer by simply reversing the signal direction.

Stray capacitance of traces and the output capacitance of switches placed in parallel reduces bandwidth, so the outputs of no more than four individual switches should be placed in parallel to maintain a high bandwidth. If more than four mux channels are needed, the 4-channel circuit should be duplicated and cascaded.

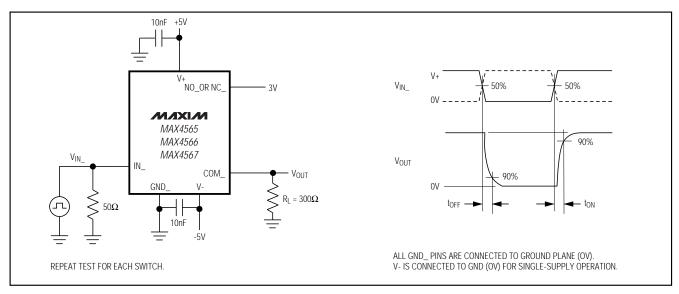

## Test Circuits/Timing Diagrams

Figure 3. Switching Time

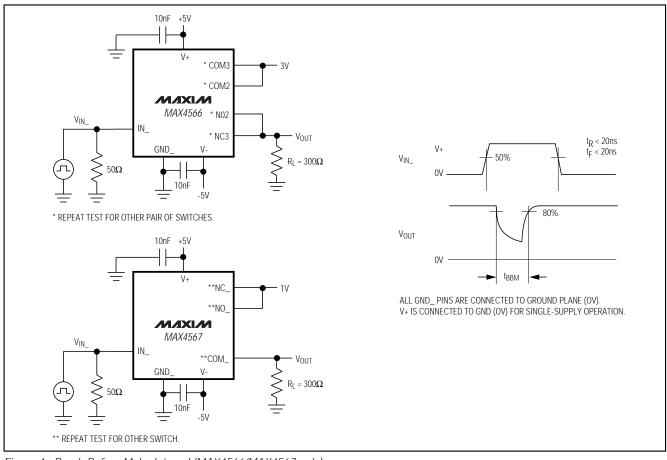

# Test Circuits/Timing Diagrams (continued)

Figure 4. Break-Before-Make Interval (MAX4566/MAX4567 only)

## Test Circuits/Timing Diagrams (continued)

Figure 5. Charge Injection

Figure 6. On Loss, Off Isolation, and Crosstalk

# Test Circuits/Timing Diagrams (continued)

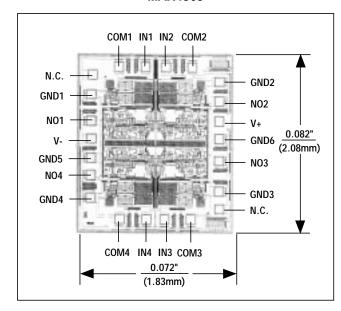

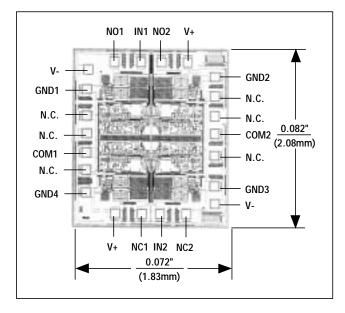

## \_Chip Topographies

#### **MAX4565**

Figure 7. NO\_, NC\_, COM\_ Capacitance

#### **MAX4566**

# N.C. — GND2 NO1 — NO2 N.C. — N.C. —

#### MAX4567

TRANSISTOR COUNT: 257

SUBSTRATE INTERNALLY CONNECTED TO V+

#### Ordering Information (continued)

| PART       | TEMP. RANGE    | PIN-PACKAGE    |

|------------|----------------|----------------|

| MAX4565CAP | 0°C to +70°C   | 20 SSOP        |

| MAX4565C/D | 0°C to +70°C   | Dice*          |

| MAX4565EPP | -40°C to +85°C | 20 Plastic DIP |

| MAX4565EWP | -40°C to +85°C | 20 Wide SO     |

| MAX4565EAP | -40°C to +85°C | 20 SSOP        |

| MAX4566CPE | 0°C to +70°C   | 16 Plastic DIP |

| MAX4566CSE | 0°C to +70°C   | 16 Narrow SO   |

| MAX4566CEE | 0°C to +70°C   | 16 QSOP        |

| MAX4566C/D | 0°C to +70°C   | Dice*          |

| MAX4566EPE | -40°C to +85°C | 16 Plastic DIP |

| MAX4566ESE | -40°C to +85°C | 16 Narrow SO   |

| TEMP. RANGE    | PIN-PACKAGE                                                                                            |

|----------------|--------------------------------------------------------------------------------------------------------|

| -40°C to +85°C | 16 QSOP                                                                                                |

| 0°C to +70°C   | 16 Plastic DIP                                                                                         |

| 0°C to +70°C   | 16 Narrow SO                                                                                           |

| 0°C to +70°C   | 16 QSOP                                                                                                |

| 0°C to +70°C   | Dice*                                                                                                  |

| -40°C to +85°C | 16 Plastic DIP                                                                                         |

| -40°C to +85°C | 16 Narrow SO                                                                                           |

| -40°C to +85°C | 16 QSOP                                                                                                |

|                | -40°C to +85°C  0°C to +70°C  0°C to +70°C  0°C to +70°C  0°C to +70°C  -40°C to +85°C  -40°C to +85°C |

<sup>\*</sup>Contact factory for dice specifications.

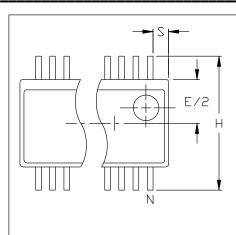

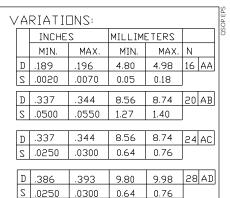

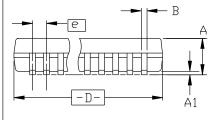

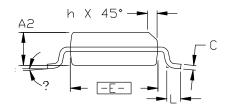

# Package Information

|     | INCH           | ES    | MILLIMETER |      |  |  |  |

|-----|----------------|-------|------------|------|--|--|--|

| DIM | MIN            | MAX   | MIN        | MAX  |  |  |  |

| Α   | .061           | .068  | 1.55       | 1.73 |  |  |  |

| A1  | .004           | .0098 | 0.127      | 0.25 |  |  |  |

| A2  | .055           | .061  | 1.40       | 1.55 |  |  |  |

| В   | .008           | .012  | 0.20       | 0.31 |  |  |  |

| С   | .0075          | .0098 | 0.19       | 0.25 |  |  |  |

| D   | SEE VARIATIONS |       |            |      |  |  |  |

| Ε   | .150           | .157  | 3.81       | 3.99 |  |  |  |

| е   | .025           | 5 BSC | 0.635 BSC  |      |  |  |  |

| Н   | .230           | .244  | 5.84       | 6.20 |  |  |  |

| h   | .010           | .016  | 0.25       | 0.41 |  |  |  |

| L   | .016           | .035  | 0.41       | 0.89 |  |  |  |

| N   | SEE VARIATIONS |       |            |      |  |  |  |

| S   | SEE VARIATIONS |       |            |      |  |  |  |

| ?   | 0*             | 8*    | 0°         | 8*   |  |  |  |

#### NOTES:

- 1. D & E DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS

- 2. MOLD FLASH OR PROTRUSIONS NOT TO EXCEED .006"

- 3. CONTROLLING DIMENSIONS: INCHES

PROPRIETARY INFORMATION

TITLE:

PACKAGE DUTLINE, QSDP, .150 INCH, .025' LEAD PIT

APPROVAL | DOCUMENT CONTROL NO. | REV | 1

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

16 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600