## **DDR2 SDRAM SORDIMM**

#### MT18HTS25672RHZ - 2GB

#### **Features**

- 200-pin, small-outline registered dual in-line memory module (SORDIMM)

- Fast data transfer rates: PC2-4200, PC2-5300, or PC2-6400

- 2GB (256 Meg x 72)

- Supports ECC error detection and correction

- $V_{DD} = 1.8V$

- $V_{DDSPD} = 3.0-3.6V$

- JEDEC-standard 1.8V I/O (SSTL\_18-compatible)

- Differential data strobe (DQS, DQS#) option

- 4*n*-bit prefetch architecture

- Multiple internal device banks for concurrent operation

- Programmable CAS latency (CL)

- Posted CAS additive latency (AL)

- WRITE latency = READ latency 1 <sup>t</sup>CK

- Programmable burst lengths (BL): 4 or 8

- · Adjustable data-output drive strength

- 64ms, 8192-cycle refresh

- On-die termination (ODT)

- Serial presence detect (SPD) with EEPROM

- Phase-lock loop (PLL) to reduce system clock line loading

- Gold edge contacts

- Dual rank, using 2Gb TwinDie™ devices

- · Halogen-free

- Combination Temp Sensor/EEPROM

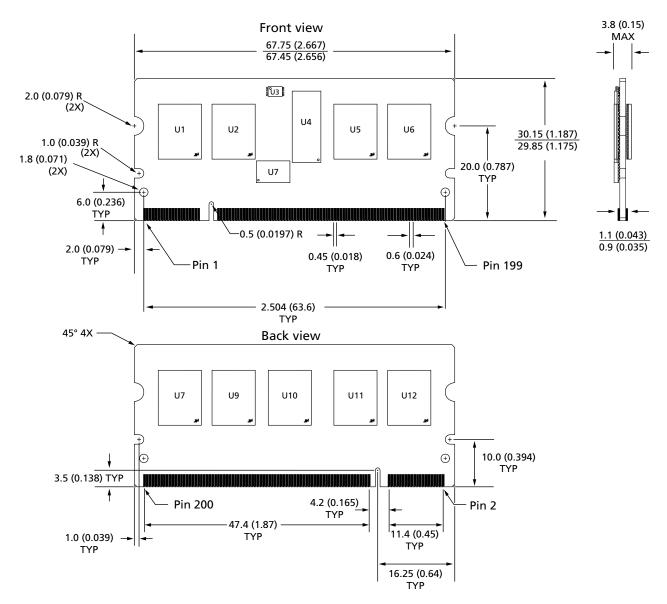

Figure 1: 200-Pin SORDIMM (R/C B)

Module height: 30mm (1.181 in)

### Options Marking

• Operating temperature

| _ | Commercial (0°C $\leq$ T <sub>A</sub> $\leq$ +70°C)                                  | None |

|---|--------------------------------------------------------------------------------------|------|

| _ | Industrial $(-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C})^1$ | I    |

|   |                                                                                      |      |

- Package

- 200-pin DIMM (Halogen-free)

Z

- Frequency/CL<sup>2</sup>

- 2.5 @ CL = 5 (DDR2-800) -80E - 2.5 @ CL = 6 (DDR2-800) -800 - 3.0ns @ CL = 5 (DDR2-667) -667

- Notes: 1. Contact Micron for industrial temperature module offerings.

- 2. CL = CAS (READ) latency; registered mode will add one clock cycle to CL.

#### **Table 1: Key Timing Parameters**

| Speed              | Industry |        | Data Ra | te (MT/s) | <sup>t</sup> RCD | <sup>t</sup> RP | <sup>t</sup> RC |      |

|--------------------|----------|--------|---------|-----------|------------------|-----------------|-----------------|------|

| Grade Nomenclature |          | CL = 6 | CL = 5  | CL = 4    | CL = 3           | (ns)            | (ns)            | (ns) |

| -80E               | PC2-6400 | 800    | 800     | 533       | 400              | 12.5            | 12.5            | 55   |

| -800               | PC2-6400 | 800    | 667     | 533       | 400              | 15              | 15              | 55   |

| -667               | PC2-5300 | -      | 667     | 553       | 400              | 15              | 15              | 55   |

| -53E               | PC2-4200 | _      | -       | 553       | 400              | 15              | 15              | 55   |

| -40E               | PC2-3200 | -      | -       | 400       | 400              | 15              | 15              | 55   |

## 2GB (x72, ECC, DR) 200-Pin DDR2 SDRAM SORDIMM Features

#### **Table 2: Addressing**

| Parameter            | 1GB                       |

|----------------------|---------------------------|

| Refresh count        | 8K                        |

| Row address          | 16K A[13:0]               |

| Device bank address  | 8 BA[2:0]                 |

| Device configuration | 2Gb TwinDie (256 Meg x 8) |

| Column address       | 1K A[9:0]                 |

| Module rank address  | 2 S#[1:0]                 |

#### Table 3: Part Numbers and Timing Parameters - 2GB Modules

Base device: MT47H256M8,<sup>1</sup> 2Gb DDR2 TwinDie SDRAM

| Part Number <sup>2</sup> | Module<br>Density | Configuration | Module<br>Bandwidth | Memory Clock/<br>Data Rate | Clock Cycles<br>(CL- <sup>t</sup> RCD- <sup>t</sup> RP) |

|--------------------------|-------------------|---------------|---------------------|----------------------------|---------------------------------------------------------|

| MT18HTS25672RH(I)Z-80E   | 2GB               | 256 Meg x 72  | 6.4 GB/s            | 2.5ns/800 MT/s             | 5-5-5                                                   |

| MT18HTS25672RH(I)Z-800   | 2GB               | 256Meg x 72   | 6.4 GB/s            | 2.5ns/800 MT/s             | 6-6-6                                                   |

| MT18HTS25672RH(I)Z-667   | 2GB               | 256 Meg x 72  | 5.3 GB/s            | 3.0ns/667 MT/s             | 5-5-5                                                   |

Notes: 1. The data sheet for the base device can be found on Micron's Web site.

2. All part numbers end with a two-place code (not shown) that designates component and PCB revisions. Consult factory for current revision codes. Example: MT18HTS25672RHZ-80E<u>M1</u>.

# 2GB (x72, ECC, DR) 200-Pin DDR2 SDRAM SORDIMM Pin Assignments

## **Pin Assignments**

**Table 4: Pin Assignments**

|     | 200-Pin SORDIMM Front |     |                 |     |                 | 200-Pin SORDIMM Back |                 |     |                 |     |                 |     |                 |     |                 |

|-----|-----------------------|-----|-----------------|-----|-----------------|----------------------|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| Pin | Symbol                | Pin | Symbol          | Pin | Symbol          | Pin                  | Symbol          | Pin | Symbol          | Pin | Symbol          | Pin | Symbol          | Pin | Symbol          |

| 1   | V <sub>REF</sub>      | 51  | DQ18            | 101 | $V_{DD}$        | 151                  | V <sub>SS</sub> | 2   | V <sub>SS</sub> | 52  | V <sub>SS</sub> | 102 | A6              | 152 | V <sub>SS</sub> |

| 3   | DQ0                   | 53  | DQ19            | 103 | A5              | 153                  | DQS5#           | 4   | DQ4             | 54  | DQ28            | 104 | A4              | 154 | DM5             |

| 5   | V <sub>SS</sub>       | 55  | V <sub>SS</sub> | 105 | A3              | 155                  | DQS5            | 6   | DQ5             | 56  | DQ29            | 106 | V <sub>DD</sub> | 156 | V <sub>SS</sub> |

| 7   | DQ1                   | 57  | DQ24            | 107 | A2              | 157                  | $V_{SS}$        | 8   | V <sub>SS</sub> | 58  | V <sub>SS</sub> | 108 | A1              | 158 | DQ46            |

| 9   | DQS0#                 | 59  | DQ25            | 109 | $V_{DD}$        | 159                  | DQ42            | 10  | DM0             | 60  | DM3             | 110 | A0              | 160 | DQ47            |

| 11  | DQS0                  | 61  | V <sub>SS</sub> | 111 | A10             | 161                  | DQ43            | 12  | V <sub>SS</sub> | 62  | V <sub>SS</sub> | 112 | BA1             | 162 | V <sub>SS</sub> |

| 13  | V <sub>SS</sub>       | 63  | DQS3#           | 113 | BA0             | 163                  | $V_{SS}$        | 14  | DQ6             | 64  | DQ30            | 114 | $V_{DD}$        | 164 | DQ52            |

| 15  | DQ2                   | 65  | DQS3            | 115 | RAS#            | 165                  | DQ48            | 16  | DQ7             | 66  | DQ31            | 116 | WE#             | 166 | DQ53            |

| 17  | DQ3                   | 67  | $V_{SS}$        | 117 | $V_{DD}$        | 167                  | DQ49            | 18  | V <sub>SS</sub> | 68  | V <sub>SS</sub> | 118 | S0#             | 168 | V <sub>SS</sub> |

| 19  | V <sub>SS</sub>       | 69  | DQ26            | 119 | CAS#            | 169                  | $V_{SS}$        | 20  | DQ12            | 70  | CB4             | 120 | ODT0            | 170 | DM6             |

| 21  | DQ8                   | 71  | DQ27            | 121 | S1#             | 171                  | DQS6#           | 22  | DQ13            | 72  | CB5             | 122 | A13             | 172 | V <sub>SS</sub> |

| 23  | DQ9                   | 73  | $V_{SS}$        | 123 | $V_{DD}$        | 173                  | DQS6            | 24  | V <sub>SS</sub> | 74  | V <sub>SS</sub> | 124 | $V_{DD}$        | 174 | DQ54            |

| 25  | V <sub>SS</sub>       | 75  | CB0             | 125 | ODT1            | 175                  | $V_{SS}$        | 26  | DM1             | 76  | DM8             | 126 | CK0             | 176 | DQ55            |

| 27  | DQS1#                 | 77  | CB1             | 127 | NC              | 177                  | DQ50            | 28  | V <sub>SS</sub> | 78  | V <sub>SS</sub> | 128 | CK0#            | 178 | $V_{SS}$        |

| 29  | DQS1                  | 79  | V <sub>SS</sub> | 129 | DQ32            | 179                  | DQ51            | 30  | DQ14            | 80  | CB6             | 130 | V <sub>SS</sub> | 180 | DQ60            |

| 31  | V <sub>SS</sub>       | 81  | DQS8#           | 131 | V <sub>SS</sub> | 181                  | V <sub>SS</sub> | 32  | DQ15            | 82  | CB7             | 132 | DQ36            | 182 | DQ61            |

| 33  | DQ10                  | 83  | DQS8            | 133 | DQ33            | 183                  | DQ56            | 34  | V <sub>SS</sub> | 84  | V <sub>SS</sub> | 134 | DQ37            | 184 | V <sub>SS</sub> |

| 35  | DQ11                  | 85  | $V_{SS}$        | 135 | DQS4#           | 185                  | DQ57            | 36  | DQ20            | 86  | CB2             | 136 | V <sub>SS</sub> | 186 | DM7             |

| 37  | V <sub>SS</sub>       | 87  | CKE0            | 137 | DQS4            | 187                  | $V_{SS}$        | 38  | DQ21            | 88  | CB3             | 138 | DM4             | 188 | DQ62            |

| 39  | DQ16                  | 89  | CKE1            | 139 | V <sub>SS</sub> | 189                  | DQS7#           | 40  | V <sub>SS</sub> | 90  | V <sub>SS</sub> | 140 | V <sub>SS</sub> | 190 | V <sub>SS</sub> |

| 41  | DQ17                  | 91  | EVENT#          | 141 | DQ34            | 191                  | DQS7            | 42  | RESET#          | 92  | BA2             | 142 | DQ38            | 192 | DQ63            |

| 43  | V <sub>SS</sub>       | 93  | V <sub>DD</sub> | 143 | DQ35            | 193                  | DQ58            | 44  | DM2             | 94  | NC              | 144 | DQ39            | 194 | SDA             |

| 45  | DQS2#                 | 95  | A12             | 145 | V <sub>SS</sub> | 195                  | V <sub>SS</sub> | 46  | V <sub>SS</sub> | 96  | A11             | 146 | V <sub>SS</sub> | 196 | SCL             |

| 47  | DQS2                  | 97  | A9              | 147 | DQ40            | 197                  | DQ59            | 48  | DQ22            | 98  | $V_{DD}$        | 148 | DQ44            | 198 | SA1             |

| 49  | V <sub>SS</sub>       | 99  | A7              | 149 | DQ41            | 199                  | $V_{\rm DDSPD}$ | 50  | DQ23            | 100 | A8              | 150 | DQ45            | 200 | SA0             |

## 2GB (x72, ECC, DR) 200-Pin DDR2 SDRAM SORDIMM Pin Descriptions

## **Pin Descriptions**

The pin description table below is a comprehensive list of all possible pins for all DDR2 modules. All pins listed may not be supported on this module. See Pin Assignments for information specific to this module.

**Table 5: Pin Descriptions**

| Symbol          | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ax              | Input | Address inputs: Provide the row address for ACTIVE commands, and the column address and auto precharge bit (A10) for READ/WRITE commands, to select one location out of the memory array in the respective bank. A10 sampled during a PRECHARGE command determines whether the PRECHARGE applies to one bank (A10 LOW, bank selected by BAx) or all banks (A10 HIGH). The address inputs also provide the op-code during a LOAD MODE command. See the Pin Assignments Table for density-specific addressing information. |

| BAx             | Input | <b>Bank address inputs:</b> Define the device bank to which an ACTIVE, READ, WRITE, or PRECHARGE command is being applied. BA define which mode register (MR0, MR1, MR2, and MR3) is loaded during the LOAD MODE command.                                                                                                                                                                                                                                                                                                |

| CKx,<br>CK#x    | Input | <b>Clock:</b> Differential clock inputs. All control, command, and address input signals are sampled on the crossing of the positive edge of CK and the negative edge of CK#.                                                                                                                                                                                                                                                                                                                                            |

| CKEx            | Input | <b>Clock enable:</b> Enables (registered HIGH) and disables (registered LOW) internal circuitry and clocks on the DDR2 SDRAM.                                                                                                                                                                                                                                                                                                                                                                                            |

| DMx             | Input | <b>Data mask (x8 devices only):</b> DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH, along with that input data, during a write access. Although DM pins are input-only, DM loading is designed to match that of the DQ and DQS pins.                                                                                                                                                                                                                                            |

| ODTx            | Input | <b>On-die termination:</b> Enables (registered HIGH) and disables (registered LOW) termination resistance internal to the DDR2 SDRAM. When enabled in normal operation, ODT is only applied to the following pins: DQ, DQS, DQS#, DM, and CB. The ODT input will be ignored if disabled via the LOAD MODE command.                                                                                                                                                                                                       |

| Par_In          | Input | Parity input: Parity bit for Ax, RAS#, CAS#, and WE#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RAS#, CAS#, WE# | Input | <b>Command inputs:</b> RAS#, CAS#, and WE# (along with S#) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RESET#          | Input | <b>Reset:</b> Asynchronously forces all registered outputs LOW when RESET# is LOW. This signal can be used during power-up to ensure that CKE is LOW and DQ are High-Z.                                                                                                                                                                                                                                                                                                                                                  |

| S#x             | Input | <b>Chip select:</b> Enables (registered LOW) and disables (registered HIGH) the command decoder.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SAx             | Input | <b>Serial address inputs:</b> Used to configure the SPD EEPROM address range on the I <sup>2</sup> C bus.                                                                                                                                                                                                                                                                                                                                                                                                                |

| SCL             | Input | <b>Serial clock for SPD EEPROM:</b> Used to synchronize communication to and from the SPD EEPROM on the I <sup>2</sup> C bus.                                                                                                                                                                                                                                                                                                                                                                                            |

| CBx             | I/O   | Check bits. Used for system error detection and correction.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DQx             | I/O   | Data input/output: Bidirectional data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DQSx,<br>DQS#x  | I/O   | <b>Data strobe:</b> Travels with the DQ and is used to capture DQ at the DRAM or the controller. Output with read data; input with write data for source synchronous operation. DQS# is only used when differential data strobe mode is enabled via the LOAD MODE command.                                                                                                                                                                                                                                               |

### 2GB (x72, ECC, DR) 200-Pin DDR2 SDRAM SORDIMM Pin Descriptions

#### **Table 5: Pin Descriptions (Continued)**

| Symbol                            | Туре                   | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA                               | I/O                    | <b>Serial data:</b> Used to transfer addresses and data into and out of the SPD EEPROM on the I <sup>2</sup> C bus.                                                                                                                                                                                                                                                               |

| RDQSx,<br>RDQS#x                  | Output                 | <b>Redundant data strobe (x8 devices only):</b> RDQS is enabled/disabled via the LOAD MODE command to the extended mode register (EMR). When RDQS is enabled, RDQS is output with read data only and is ignored during write data. When RDQS is disabled, RDQS becomes data mask (see DMx). RDQS# is only used when RDQS is enabled and differential data strobe mode is enabled. |

| Err_Out#                          | Output<br>(open drain) | Parity error output: Parity error found on the command and address bus.                                                                                                                                                                                                                                                                                                           |

| V <sub>DD</sub> /V <sub>DDQ</sub> | Supply                 | <b>Power supply:</b> 1.8V $\pm$ 0.1V. The component $V_{DD}$ and $V_{DDQ}$ are connected to the module $V_{DD}$ .                                                                                                                                                                                                                                                                 |

| V <sub>DDSPD</sub>                | Supply                 | SPD EEPROM power supply: 1.7–3.6V.                                                                                                                                                                                                                                                                                                                                                |

| V <sub>REF</sub>                  | Supply                 | Reference voltage: V <sub>DD</sub> /2.                                                                                                                                                                                                                                                                                                                                            |

| V <sub>SS</sub>                   | Supply                 | Ground.                                                                                                                                                                                                                                                                                                                                                                           |

| NC                                | _                      | No connect: These pins are not connected on the module.                                                                                                                                                                                                                                                                                                                           |

| NF                                | -                      | <b>No function:</b> These pins are connected within the module, but provide no functionality.                                                                                                                                                                                                                                                                                     |

| NU                                | _                      | Not used: These pins are not used in specific module configurations/operations.                                                                                                                                                                                                                                                                                                   |

| RFU                               | _                      | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                          |

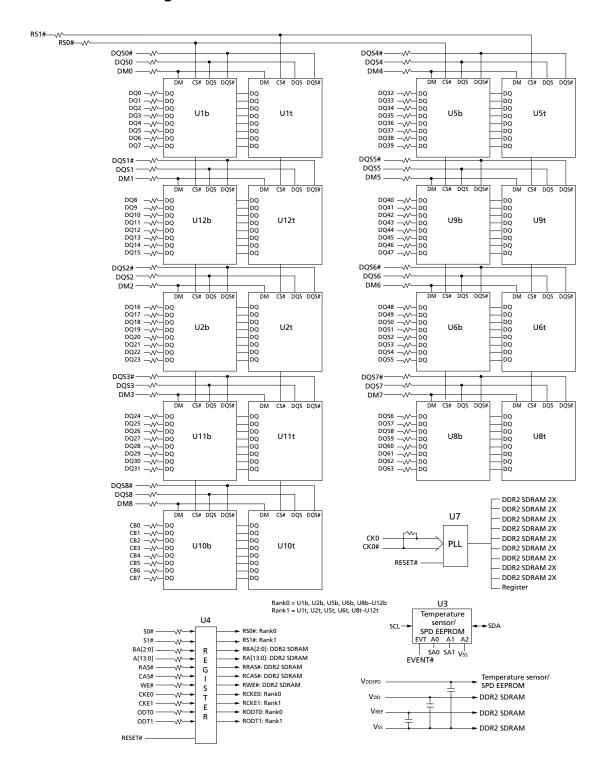

### **Functional Block Diagram**

**Figure 2: Functional Block Diagram**

## 2GB (x72, ECC, DR) 200-Pin DDR2 SDRAM SORDIMM General Description

### **General Description**

DDR2 SDRAM modules are high-speed, CMOS dynamic random access memory modules that use internally configured 4 or 8-bank DDR2 SDRAM devices. DDR2 SDRAM modules use DDR architecture to achieve high-speed operation. DDR2 architecture is essentially a 4*n*-prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the DDR2 SDRAM module effectively consists of a single 4*n*-bit-wide, one-clock-cycle data transfer at the internal DRAM core and eight corresponding *n*-bit-wide, one-half-clock-cycle data transfers at the I/O pins.

DDR2 modules use two sets of differential signals: DQS, DQS# to capture data and CK and CK# to capture commands, addresses, and control signals. Differential clocks and data strobes ensure exceptional noise immunity for these signals and provide precise crossing points to capture input signals. A bidirectional data strobe (DQS, DQS#) is transmitted externally, along with data, for use in data capture at the receiver. DQS is a strobe transmitted by the DDR2 SDRAM device during READs and by the memory controller during WRITEs. DQS is edge-aligned with data for READs and center-aligned with data for WRITEs.

DDR2 SDRAM modules operate from a differential clock (CK and CK#); the crossing of CK going HIGH and CK# going LOW will be referred to as the positive edge of CK. Commands (address and control signals) are registered at every positive edge of CK. Input data is registered on both edges of DQS, and output data is referenced to both edges of DQS, as well as to both edges of CK.

#### **Serial Presence-Detect EEPROM Operation**

DDR2 SDRAM modules incorporate serial presence-detect. The SPD data is stored in a 256-byte EEPROM. The first 128 bytes are programmed by Micron to identify the module type and various SDRAM organizations and timing parameters. The remaining 128 bytes of storage are available for use by the customer. System READ/WRITE operations between the master (system logic) and the slave EEPROM device occur via a standard I<sup>2</sup>C bus using the DIMM's SCL (clock) SDA (data), and SA (address) pins. Write protect (WP) is connected to V<sub>SS</sub>, permanently disabling hardware write protection.

### **Register and PLL Operation**

DDR2 SDRAM modules operate in registered mode, where the command/address input signals are latched in the registers on the rising clock edge and sent to the DDR2 SDRAM devices on the following rising clock edge (data access is delayed by one clock cycle). A phase-lock loop (PLL) on the module receives and redrives the differential clock signals (CK, CK#) to the DDR2 SDRAM devices. The registers and PLL minimize system and clock loading. PLL clock timing is defined by JEDEC specifications and ensured by use of the JEDEC clock reference board. Registered mode will add one clock cycle to CL.

### **Temperature Sensor**

An on-board temperature sensor provides the ability to monitor the module temperature along with monitoring alarms. Programmable registers can be used to specify temperature events and critical boundaries. An EVENT# pin is used to signal when different conditions occur based on how the registers are defined.

# 2GB (x72, ECC, DR) 200-Pin DDR2 SDRAM SORDIMM Electrical Specifications

### **Electrical Specifications**

Stresses greater than those listed may cause permanent damage to the module. This is a stress rating only, and functional operation of the module at these or any other conditions outside those indicated in the device data sheet are not implied. Exposure to absolute maximum rating conditions for extended periods may adversely affect reliability.

**Table 6: Absolute Maximum Ratings**

| Symbol                             | Parameter                                                                                                                                                                                    |                                                      | Min        | Max | Units |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------|-----|-------|

| V <sub>DD</sub>                    | V <sub>DD</sub> supply voltage relative to V <sub>SS</sub>                                                                                                                                   |                                                      | -0.5       | 2.3 | V     |

| V <sub>IN</sub> , V <sub>OUT</sub> | Voltage on any pin relative to V <sub>SS</sub>                                                                                                                                               |                                                      | -0.5       | 2.3 | V     |

| I <sub>I</sub>                     | Input leakage current; Any input $0V \le V_{IN} \le V_{DD}$ ; $V_{REF}$ input $0V \le V_{IN} \le 0.95V$ ; (All other                                                                         | Address inputs, RAS#, CAS#,<br>WE#, S#, CKE, ODT, BA | <b>-</b> 5 | 5   | μА    |

|                                    | Voltage on any pin relative to $V_{SS}$<br>Input leakage current; Any input $0V \le V_{IN} \le V_{DD}$ ; $V_{REF}$ input $0V \le V_{IN} \le 0.95V$ ; (All other pins not under test = $0V$ ) | CK0, CK0#                                            | -250       | 250 |       |

|                                    |                                                                                                                                                                                              | DM                                                   | -10        | 10  |       |

| I <sub>OZ</sub>                    |                                                                                                                                                                                              | DQ, DQS, DQS#                                        | -10        | 10  | μА    |

| I <sub>VREF</sub>                  | $V_{REF}$ leakage current; $V_{REF}$ = valid $V_{REF}$ level                                                                                                                                 |                                                      | -36        | 36  | μΑ    |

| T <sub>A</sub>                     | Module ambient operating temperature                                                                                                                                                         | Commercial                                           | 0          | 70  | °C    |

|                                    |                                                                                                                                                                                              | Industrial                                           | -40        | 85  | °C    |

| T <sub>C</sub> <sup>1</sup>        | DDR2 SDRAM component operating tem-                                                                                                                                                          | Commercial                                           | 0          | 85  | °C    |

|                                    | perature <sup>2</sup>                                                                                                                                                                        | Industrial                                           | -40        | 95  | °C    |

- Notes: 1. The refresh rate is required to double when T<sub>C</sub> exceeds 85°C.

- 2. For further information, refer to technical note TN-00-08: "Thermal Applications," available on Micron's Web site.

## 2GB (x72, ECC, DR) 200-Pin DDR2 SDRAM SORDIMM DRAM Operating Conditions

### **DRAM Operating Conditions**

Recommended AC operating conditions are given in the DDR2 component data sheets. Component specifications are available on Micron's Web site. Module speed grades correlate with component speed grades.

**Table 7: Module and Component Speed Grades**

DDR2 components may exceed the listed module speed grades; module may not be available in all listed speed grades

| Module Speed Grade | Component Speed Grade |

|--------------------|-----------------------|

| -1GA               | -187E                 |

| -80E               | -25E                  |

| -800               | -25                   |

| -667               | -3                    |

| -53E               | -37E                  |

| -40E               | -5E                   |

### **Design Considerations**

#### **Simulations**

Micron memory modules are designed to optimize signal integrity through carefully designed terminations, controlled board impedances, routing topologies, trace length matching, and decoupling. However, good signal integrity starts at the system level. Micron encourages designers to simulate the signal characteristics of the system's memory bus to ensure adequate signal integrity of the entire memory system.

#### Power

Operating voltages are specified at the DRAM, not at the edge connector of the module. Designers must account for any system voltage drops at anticipated power levels to ensure the required supply voltage is maintained.

### **IDD Specifications**

#### Table 8: DDR2 I<sub>DD</sub> Specifications and Conditions – 2GB (Die Revision H)

Values shown for MT47H256M8 DDR2 SDRAM only and are computed from values specified in the 2Gb TwinDie(256 Meg x 8) component data sheet

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                | Combined<br>Symbol | -80E    | -667 | Units |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------|---------|------|-------|

| <b>Operating one bank active-precharge current:</b> ${}^{t}CK = {}^{t}CK (I_{DD}), {}^{t}I_{DD}, {}^{t}RAS = {}^{t}RAS MIN (I_{DD}); CKE is HIGH, S# is HIGH between valid of Address bus inputs are switching; Data bus inputs are switching$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I <sub>CDD0</sub>              | 648                | 603     | mA   |       |

| Operating one bank active-read-precharge current: $I_{OUT} = 0 \text{ m/s}$ = CL ( $I_{DD}$ ), AL = 0; ${}^{\text{t}}\text{CK} = {}^{\text{t}}\text{CK}$ ( $I_{DD}$ ), ${}^{\text{t}}\text{RC} = {}^{\text{t}}\text{RC}$ ( $I_{DD}$ ), ${}^{\text{t}}\text{RAS} = {}^{\text{t}}\text{RAS}$ MIN ( $I_{\text{t}}$ tRCD ( $I_{DD}$ ); CKE is HIGH, S# is HIGH between valid commands; Address are switching; Data pattern is same as $I_{DD4W}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I <sub>CDD1</sub>              | 738                | 693     | mA   |       |

| <b>Precharge power-down current:</b> All device banks idle; <sup>t</sup> CK = <sup>t</sup> CK LOW; Other control and address bus inputs are stable; Data bus inp ing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                | I <sub>CDD2P</sub> | 126     | 126  | mA    |

| <b>Precharge quiet standby current:</b> All device banks idle; <sup>t</sup> CK = <sup>t</sup> CH HIGH, S# is HIGH; Other control and address bus inputs are stable; I puts are floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I <sub>CDD2Q</sub>             | 279                | 279     | mA   |       |

| <b>Precharge standby current:</b> All device banks idle; ${}^{t}CK = {}^{t}CK (I_{DD})$ ; S# is HIGH; Other control and address bus inputs are switching; Dat are switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                | I <sub>CDD2N</sub> | 315     | 279  | mA    |

| <b>Active power-down current:</b> All device banks open; <sup>t</sup> CK = <sup>t</sup> CK (I <sub>DD</sub> ); CKE is LOW; Other control and address bus inputs are stable; Data bus inputs are floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Fast PDN<br>exit<br>MR[12] = 0 | I <sub>CDD3P</sub> | 243 198 |      | mA    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Slow PDN<br>exit<br>MR[12] = 1 |                    | 153     | 153  |       |

| <b>Active standby current:</b> All device banks open; ${}^{t}CK = {}^{t}CK (I_{DD})$ , ${}^{t}R$ , MAX $(I_{DD})$ , ${}^{t}RP = {}^{t}RP (I_{DD})$ ; CKE is HIGH, S# is HIGH between valid condition of their control and address bus inputs are switching; Data bus inputs ing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mmands;                        | I <sub>CDD3N</sub> | 360     | 333  | mA    |

| <b>Operating burst write current:</b> All device banks open; Continuou writes; BL = 4, CL = CL ( $I_{DD}$ ), AL = 0; ${}^{t}CK = {}^{t}CK$ ( $I_{DD}$ ), ${}^{t}RAS = {}^{t}RAS$ MAX ${}^{t}RP$ ( $I_{DD}$ ); CKE is HIGH, S# is HIGH between valid commands; Address are switching; Data bus inputs are switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\langle (I_{DD}), {}^{t}RP =$ | I <sub>CDD4W</sub> | 1188    | 1098 | mA    |

| <b>Operating burst read current:</b> All device banks open; Continuous $I_{OUT} = 0$ mA; $BL = 4$ , $CL = CL (I_{DD})$ , $AL = 0$ ; ${}^{t}CK = {}^{t}CK (I_{DD})$ , ${}^{t}RAS = {}^{t}RAS (I_{DD})$ ; $CKE = {}^{t}RB (I_{$ | MAX (I <sub>DD</sub> ),        | I <sub>CDD4R</sub> | 1143    | 1053 | mA    |

| <b>Burst refresh current:</b> <sup>t</sup> CK = <sup>t</sup> CK (I <sub>DD</sub> ); REFRESH command at every terval; CKE is HIGH, S# is HIGH between valid commands; Other condress bus inputs are switching; Data bus inputs are switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                | I <sub>CDD5</sub>  | 1368    | 1323 | mA    |

| <b>Self refresh current:</b> CK and CK# at 0V; CKE $\leq$ 0.2V; Other control bus inputs are floating; Data bus inputs are floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | and address                    | I <sub>CDD6</sub>  | 126     | 126  | mA    |

# 2GB (x72, ECC, DR) 200-Pin DDR2 SDRAM SORDIMM IDD Specifications

#### Table 8: DDR2 I<sub>DD</sub> Specifications and Conditions – 2GB (Die Revision H) (Continued)

Values shown for MT47H256M8 DDR2 SDRAM only and are computed from values specified in the 2Gb TwinDie(256 Meg x 8) component data sheet

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                           | Combined<br>Symbol | -80E | -667 | Units |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|------|-------|

| <b>Operating bank interleave read current:</b> All device banks interleaving reads; $I_{OUT} = 0$ mA; $BL = 4$ , $CL = CL (I_{DD})$ , $AL = {}^tRCD (I_{DD}) - 1 \times {}^tCK (I_{DD})$ ; ${}^tCK = {}^tCK (I_{DD})$ , ${}^tRC = {}^tRC (I_{DD})$ , ${}^tRCD = {}^tRCD (I_{DD})$ ; $CKE$ is HIGH, S# is HIGH between valid commands; Address bus inputs are stable during deselects; Data bus inputs are switching | I <sub>CDD7</sub>  | 1953 | 1728 | mA    |

#### Table 9: DDR2 I<sub>DD</sub> Specifications and Conditions – 2GB (Die Revision M)

Values shown for MT47H256M8 DDR2 SDRAM only and are computed from values specified in the 2Gb TwinDie(256 Meg x 8) component data sheet

| Parameter                                                                                                                                                                                                                                                                                                                                                                                |                                         | Combined<br>Symbol | -80E | -667 | Units |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------|------|------|-------|

| <b>Operating one bank active-precharge current:</b> ${}^tCK = {}^tCK (I_{DD}), {}^tI_{DD}, {}^tRAS = {}^tRAS MIN (I_{DD}); CKE is HIGH, S# is HIGH between valid of Address bus inputs are switching; Data bus inputs are switching$                                                                                                                                                     | I <sub>CDD0</sub>                       | 720                | 675  | mA   |       |

| Operating one bank active-read-precharge current: $I_{OUT} = 0 \text{ m/s}$ = CL ( $I_{DD}$ ), AL = 0; ${}^{\text{t}}$ CK = ${}^{\text{t}}$ CK ( $I_{DD}$ ), ${}^{\text{t}}$ RC = ${}^{\text{t}}$ RC ( $I_{DD}$ ), ${}^{\text{t}}$ RAS = ${}^{\text{t}}$ RAS MIN ( $I_{DD}$ ); CKE is HIGH, S# is HIGH between valid commands; Address are switching; Data pattern is same as $I_{DD4W}$ | I <sub>CDD1</sub>                       | 810                | 764  | mA   |       |

| <b>Precharge power-down current:</b> All device banks idle; <sup>t</sup> CK = <sup>t</sup> CK LOW; Other control and address bus inputs are stable; Data bus inping                                                                                                                                                                                                                      |                                         | I <sub>CDD2P</sub> | 180  | 180  | mA    |

| <b>Precharge quiet standby current:</b> All device banks idle; <sup>t</sup> CK = <sup>t</sup> CH HIGH, S# is HIGH; Other control and address bus inputs are stable; I puts are floating                                                                                                                                                                                                  |                                         | I <sub>CDD2Q</sub> | 306  | 306  | mA    |

| <b>Precharge standby current:</b> All device banks idle; <sup>t</sup> CK = <sup>t</sup> CK (I <sub>DD</sub> ); S# is HIGH; Other control and address bus inputs are switching; Dat are switching                                                                                                                                                                                         |                                         | I <sub>CDD2N</sub> | 387  | 351  | mA    |

| <b>Active power-down current:</b> All device banks open; ${}^{t}CK = {}^{t}CK$ ( $I_{DD}$ ); CKE is LOW; Other control and address bus inputs are stable; Data bus inputs are floating                                                                                                                                                                                                   | Fast PDN<br>exit<br>MR[12] = 0          | I <sub>CDD3P</sub> | 360  | 342  | mA    |

|                                                                                                                                                                                                                                                                                                                                                                                          | Slow PDN<br>exit<br>MR[12] = 1          |                    | 270  | 270  |       |

| <b>Active standby current:</b> All device banks open; ${}^{t}CK = {}^{t}CK$ ( $I_{DD}$ ), ${}^{t}R$ . MAX ( $I_{DD}$ ), ${}^{t}RP = {}^{t}RP$ ( $I_{DD}$ ); CKE is HIGH, S# is HIGH between valid con Other control and address bus inputs are switching; Data bus inputs ing                                                                                                            | I <sub>CDD3N</sub>                      | 432                | 405  | mA   |       |

| <b>Operating burst write current:</b> All device banks open; Continuou writes; BL = 4, CL = CL ( $I_{DD}$ ), AL = 0; ${}^{t}CK = {}^{t}CK (I_{DD})$ , ${}^{t}RAS = {}^{t}RAS$ MAX ${}^{t}RP (I_{DD})$ ; CKE is HIGH, S# is HIGH between valid commands; Address are switching; Data bus inputs are switching                                                                             | Κ (I <sub>DD</sub> ), <sup>t</sup> RP = | I <sub>CDD4W</sub> | 1260 | 1170 | mA    |

## 2GB (x72, ECC, DR) 200-Pin DDR2 SDRAM SORDIMM IDD Specifications

#### Table 9: DDR2 I<sub>DD</sub> Specifications and Conditions – 2GB (Die Revision M) (Continued)

Values shown for MT47H256M8 DDR2 SDRAM only and are computed from values specified in the 2Gb TwinDie(256 Meg x 8) component data sheet

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                           | Combined<br>Symbol | -80E | -667 | Units |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|------|-------|

| <b>Operating burst read current:</b> All device banks open; Continuous burst read, $I_{OUT} = 0$ mA; $BL = 4$ , $CL = CL (I_{DD})$ , $AL = 0$ ; ${}^{t}CK = {}^{t}CK (I_{DD})$ , ${}^{t}RAS = {}^{t}RAS MAX (I_{DD})$ , ${}^{t}RP = {}^{t}RP (I_{DD})$ ; CKE is HIGH, S# is HIGH between valid commands; Address bus inputs are switching; Data bus inputs are switching                                            | I <sub>CDD4R</sub> | 1215 | 1125 | mA    |

| <b>Burst refresh current:</b> ${}^{t}CK = {}^{t}CK (I_{DD});$ REFRESH command at every ${}^{t}RFC (I_{DD})$ interval; CKE is HIGH, S# is HIGH between valid commands; Other control and address bus inputs are switching; Data bus inputs are switching                                                                                                                                                             | I <sub>CDD5</sub>  | 1530 | 1485 | mA    |

| <b>Self refresh current:</b> CK and CK# at 0V; CKE ≤ 0.2V; Other control and address bus inputs are floating; Data bus inputs are floating                                                                                                                                                                                                                                                                          | I <sub>CDD6</sub>  | 126  | 126  | mA    |

| <b>Operating bank interleave read current:</b> All device banks interleaving reads; $I_{OUT} = 0$ mA; $BL = 4$ , $CL = CL (I_{DD})$ , $AL = {}^tRCD (I_{DD}) - 1 \times {}^tCK (I_{DD})$ ; ${}^tCK = {}^tCK (I_{DD})$ , ${}^tRC = {}^tRC (I_{DD})$ , ${}^tRCD = {}^tRCD (I_{DD})$ ; $CKE$ is HIGH, S# is HIGH between valid commands; Address bus inputs are stable during deselects; Data bus inputs are switching | I <sub>CDD7</sub>  | 2025 | 1800 | mA    |

# 2GB (x72, ECC, DR) 200-Pin DDR2 SDRAM SORDIMM Register and PLL Specifications

### **Register and PLL Specifications**

#### **Table 10: Register Specifications**

SSTU32872 devices or equivalent

| Parameter                                  | Symbol              | Pins                        | Condition                                                                                                                                                                                                                                                                   | Min                        | Max                        | Units |

|--------------------------------------------|---------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|-------|

| DC high-level input voltage                | V <sub>IH(DC)</sub> | Control, command, address   | SSTL_18                                                                                                                                                                                                                                                                     | V <sub>REF(DC)</sub> + 125 | V <sub>DDQ</sub> + 250     | mV    |

| DC low-level input voltage                 | V <sub>IL(DC)</sub> | Control, command, address   | SSTL_18                                                                                                                                                                                                                                                                     | 0                          | V <sub>REF(DC)</sub> - 125 | mV    |

| AC high-level input voltage                | V <sub>IH(AC)</sub> | Control, command, address   | SSTL_18                                                                                                                                                                                                                                                                     | V <sub>REF(DC)</sub> + 250 | V <sub>DD</sub>            | mV    |

| AC low-level input voltage                 | V <sub>IL(AC)</sub> | Control, command, address   | SSTL_18                                                                                                                                                                                                                                                                     | 0                          | V <sub>REF(DC)</sub> - 250 | mV    |

| Output high voltage                        | V <sub>OH</sub>     | Parity output               | SSTL_18                                                                                                                                                                                                                                                                     | 1.2                        | -                          | V     |

| Output low voltage                         | V <sub>OL</sub>     | Parity output               | SSTL_18                                                                                                                                                                                                                                                                     | _                          | 0.5                        | V     |