# 100 MHz Differential Buffer for PCI Express and SATA

#### **Features**

- Two differential 0.7V clock output pairs

- OE# input for enabling SRC outputs

- Individual OE controls

- Low CTC jitter (< 50 ps)

- Spread Aware

- 3.3V operation

- Industrial Temperature Grade -40°C to +85°C

- 16-pin TSSOP package

## **Functional Description**

The SL28DB200 is a differential buffer capable of distributing the Serial Reference Clock (SRC) for PCI Express Gen2 and SATA implementations. The buffer enables the application system to control the distribution of the SRC.

## **Applications**

- Network/Media Attached Storage

- Routers/IP Gateways

- Multi-function Printers

## **Block Diagram**

# OE1# OE2# Output Control Output Buffer SRC1 SRC1# SRC2 SRC1N#

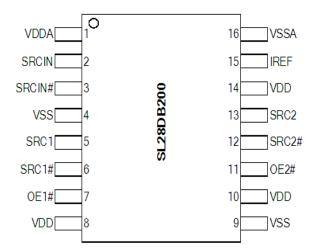

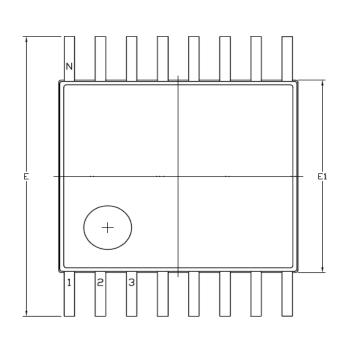

# **Pin Configuration**

16 TSSOP

# **Pin Description**

| Pin       | Name                | Type  | Description                                                                                 |

|-----------|---------------------|-------|---------------------------------------------------------------------------------------------|

| 2,3       | SRCIN, SRCIN#       | I,DIF | 0.7V Differential inputs                                                                    |

| 5,6,13,12 | SRC[1:2], SRC[1:2]# | O,DIF | 0.7V Differential Clock Outputs                                                             |

| 7,11      | OE[1:2]#            | I,SE  | 3.3V LVTTL input for enabling differential outputs                                          |

| 15        | IREF                | I     | A precision resistor 475 ohm is attached to this pin to set the differential output current |

| 1         | VDDA                | PWR   | 3.3V Power Supply                                                                           |

| 16        | VSSA                | GND   | Ground                                                                                      |

| 8,10,14   | VDD                 | PWR   | 3.3V power supply for outputs                                                               |

| 4,9       | VSS                 | GND   | Ground for outputs                                                                          |

Notes: I=Input, O=Output, DIF=Differential signal, SE=Single Ended, PWR=Power input, GND=Ground

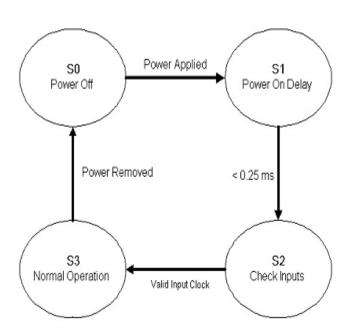

Table 1. Buffer Power-up State Machine

| State | Description                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------|

| S0    | 3.3V Buffer power off                                                                                                  |

| S1    | After 3.3V supply is detected to rise above 1.8V - 2.0V, the buffer enters state 1 and initiates a 0.2-ms–0.3-ms delay |

| S2    | Buffer waits for a valid clock on the SRCIN input                                                                      |

| S3    | Once a valid input is detected, the buffer enters state 3 and enables outputs for normal operation                     |

Figure 1. Buffer Power-up State Diagram

## **Output Enable Clarification**

OE# functionality allows for enabling and disabling individual outputs. OE1# and OE2# are Active LOW inputs. Disabling the outputs may be implemented by deasserting the OE# input pin. If the OE# pin is deasserted, the output of interest will be tri-stated. (The assertion and deassertion of this signal is absolutely asynchronous.)

#### **OE** Assertion

All differential outputs that were tri-stated will resume normal operation in a glitch-free manner. The maximum latency from the assertion to active outputs is between 2–6 SRC clock periods. In addition, SRC clocks will be driven high within 15 ns of OE# assertion to a voltage greater than 200 mV

#### **OE** Deassertion

The impact of deasserting OE# is that each corresponding output will transition from normal operation to tri-state in a glitch-free manner. The maximum latency from the deassertion to tri-stated outputs is between 2–6 DIF clock periods.

**Table 2. OE Functionality**

| OE# | SRC,SRC#  |

|-----|-----------|

| 0   | Enable    |

| 1   | Tri-State |

#### **Absolute Maximum Conditions**

| Parameter          | Description                                       | Condition                   | Min. | Max.                  | Unit |

|--------------------|---------------------------------------------------|-----------------------------|------|-----------------------|------|

| VDD                | Core Supply Voltage                               |                             | -0.5 | 4.6                   | V    |

| VDDA               | Analog Supply Voltage                             |                             | -0.5 | 4.6                   | V    |

| V <sub>IN</sub>    | Input Voltage                                     | Relative to V <sub>SS</sub> | -0.5 | V <sub>DD</sub> + 0.5 | VDC  |

| T <sub>S</sub>     | Temperature, Storage                              | Non-functional              | -65  | +150                  | °C   |

| T <sub>A</sub>     | Temperature, Operating Ambient (Commercial Grade) | Functional                  | 0    | 85                    | °C   |

| T <sub>A</sub>     | Temperature, Operating Ambient (Industrial Grade) | Functional                  | -40  | 85                    | °C   |

| T <sub>J</sub>     | Temperature, Junction                             | Functional                  |      | 150                   | °C   |

| ESD <sub>HBM</sub> | ESD Protection (Human Body Model)                 | JEDEC (JESD 22 - A114)      | 2000 | _                     | V    |

| UL-94              | Flammability Rating                               | UL (Class)                  | V-0  |                       |      |

| MSL                | Moisture Sensitivity Level                        |                             |      |                       |      |

## **DC Electrical Specifications**

| Parameter                | Description                | Condition                                                                | Min.           | Max.                  | Unit |

|--------------------------|----------------------------|--------------------------------------------------------------------------|----------------|-----------------------|------|

| VDDA <sub>,</sub><br>VDD | 3.3V Operating Voltage     | $3.3 \pm 5\%$                                                            | 3.135          | 3.465                 | V    |

| $V_{IL}$                 | 3.3V Input Low Voltage     |                                                                          | $V_{SS} - 0.5$ | 0.8                   | V    |

| $V_{IH}$                 | 3.3V Input High Voltage    |                                                                          | 2.0            | V <sub>DD</sub> + 0.5 | V    |

| I <sub>IL</sub>          | Input Low Leakage Current  | except internal pull-up resistors, 0 < V <sub>IN</sub> < V <sub>DD</sub> | <b>-</b> 5     |                       | μΑ   |

| I <sub>IH</sub>          | Input High Leakage Current | except internal pull-down resistors, $0 < V_{IN} < V_{DD}$               |                | 5                     | μΑ   |

| C <sub>IN</sub>          | Input Pin Capacitance      |                                                                          | 1.5            | 5                     | pF   |

| C <sub>OUT</sub>         | Output Pin Capacitance     |                                                                          |                | 6                     | pF   |

| L <sub>IN</sub>          | Pin Inductance             |                                                                          | _              | 7                     | nΗ   |

| I <sub>DD3.3V</sub>      | Dynamic Supply Current     | At max. load, Full Active, at 100MHz                                     | _              | 60                    | mA   |

# **AC Electrical Specifications**

All measurements at VDD (typical) = 3.3V,  $T_A = 25$ °C unless otherwise stated

| Parameter                       | Description Condition                      |                                                                             | Min.   | Max.                    | Unit |

|---------------------------------|--------------------------------------------|-----------------------------------------------------------------------------|--------|-------------------------|------|

| SRCIN at 0                      | .7V                                        |                                                                             |        |                         |      |

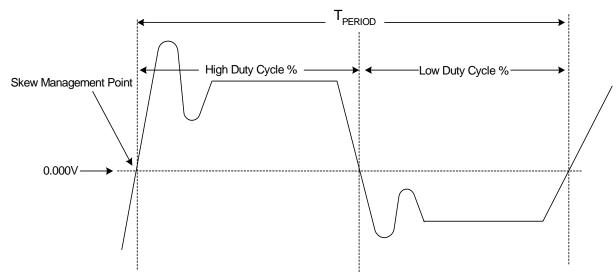

| T <sub>PERIOD</sub>             | Average Period                             | Measured at crossing point V <sub>OX</sub>                                  | 9.9970 | 10.0533                 | ns   |

| T <sub>ABSMIN-IN</sub>          | Absolute minimum clock periods             | Measured at crossing point V <sub>OX</sub>                                  | 9.8720 |                         | ns   |

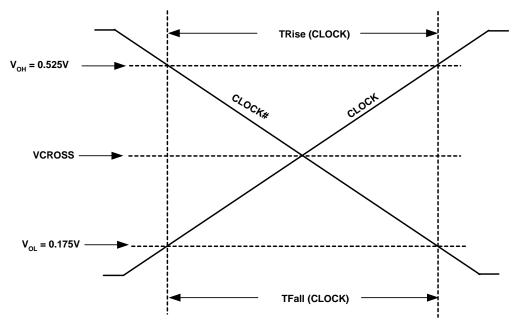

| T <sub>R</sub> / T <sub>F</sub> | SRC and SRC# Rise and Fall Times           | Single ended measurement: $V_{OL} = 0.175$ to $V_{OH} = 0.525V$ (Averaged)  | 0.6    | 4                       | V/ns |

| $V_{IH}$                        | Differential Input High Voltage            |                                                                             | 150    |                         | mV   |

| $V_{IL}$                        | Differential Input Low Voltage             |                                                                             |        | -150                    | mV   |

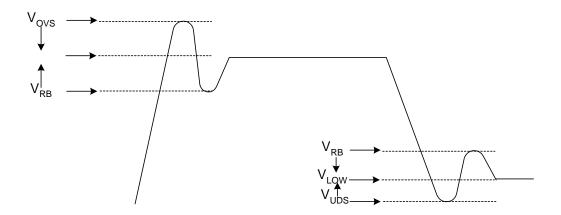

| V <sub>OX</sub>                 | Crossing Point Voltage at 0.7V Swing       | Single-ended measurement                                                    | 250    | 550                     | mV   |

| $\Delta V_{OX}$                 | Vcross Variation over all edges            | Single-ended measurement                                                    |        | 140                     | mV   |

| $V_{RB}$                        | Differential Ringback Voltage              |                                                                             | -100   | 100                     | mV   |

| T <sub>STABLE</sub>             | Time before ringback allowed               |                                                                             | 500    |                         | ps   |

| $V_{MAX}$                       | Absolute maximum input voltage             |                                                                             |        | 1.15                    | V    |

| V <sub>MIN</sub>                | Absolute minimum input voltage             |                                                                             | -0.3   |                         | V    |

| T <sub>DC</sub>                 | SRC and SRC# Duty Cycle                    | Measured at crossing point V <sub>OX</sub>                                  | 45     | 55                      | %    |

| T <sub>RFM</sub>                | Rise/Fall Matching                         | Determined as a fraction of $2*(T_R - T_F)/(T_R + T_F)$                     | _      | 20                      | %    |

| SRC at 0.7                      | V                                          |                                                                             |        | l                       |      |

| F <sub>IN</sub>                 | Input Frequency                            |                                                                             | 90     | 210                     | MHz  |

| F <sub>ERROR</sub>              | Input/Output Frequency Error               |                                                                             | _      | 0                       | ppm  |

| T <sub>DC</sub>                 | SRC and SRC# Duty Cycle                    | Measured at crossing point V <sub>OX</sub>                                  | 45     | 55                      | %    |

| T <sub>PERIOD</sub>             | Average Period                             | Measured at crossing point V <sub>OX</sub> at 100 MHz                       | 9.9970 | 10.0533                 | ns   |

| T <sub>R</sub> / T <sub>F</sub> | SRC[1:2] and SRC[1:2]# Rise and Fall Times | Single-ended measurement: $V_{OL} = 0.175$ to $V_{OH} = 0.525V$ (Averaged)  | 175    | 700                     | ps   |

| T <sub>RFM</sub>                | Rise/Fall Matching                         | Determined as a fraction of $2 * (T_R - T_F)/(T_R + T_F)$                   | _      | 20                      | %    |

| $\Delta T_R / \Delta T_F$       | Rise and Fall Time Variation Variation     | Single-ended measurement: $V_{OL} = 0.175$ to $V_{OH} = 0.525V$ (Real Time) | _      | 125                     | ps   |

| $V_{HIGH}$                      | Voltage High                               | Single-ended measurement                                                    | 660    | 850                     | mv   |

| $V_{LOW}$                       | Voltage Low                                | Single-ended measurement                                                    | -150   | _                       | mv   |

| $V_{OX}$                        | Crossing Point Voltage at 0.7V Swing       | Single-ended measurement                                                    | 250    | 550                     | mv   |

| $\Delta V_{OX}$                 | Vcross Variation over all edges            | Single-ended measurement                                                    | _      | 140                     | mV   |

| V <sub>OVS</sub>                | Maximum Overshoot Voltage                  | Single-ended measurement                                                    | _      | V <sub>HIGH</sub> + 0.3 | V    |

| V <sub>UDS</sub>                | Minimum Undershoot Voltage                 | Single-ended measurement                                                    | _      | -0.3                    | V    |

| V <sub>RB</sub>                 | Ring Back Voltage                          | Single-ended measurement                                                    | 0.2    | N/A                     | V    |

| T <sub>CCJ</sub>                | Cycle to Cycle Jitter                      | Jitter is additive                                                          | _      | 50                      | ps   |

| T <sub>SKEW</sub>               | Any SRC/SRC# to SRC/SRC# Clock<br>Skew     | Measured at crossing point V <sub>OX</sub>                                  | -      | 50                      | ps   |

| T <sub>PD</sub>                 | Input to output skew                       | Measured at crossing point V <sub>OX</sub>                                  | 2.5    | 4.5                     | ns   |

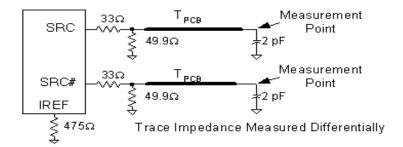

# **Test and Measurement Setup**

**Figure 1. Differential Clock Termination**

# **Switching Waveforms**

Figure 2. Single-Ended Measurement Points for TRise and TFall

Figure 3. Single-ended Measurement Points for  $V_{\text{OVS}}$ ,  $V_{\text{UDS}}$  and  $V_{\text{RB}}$

Figure 4. Differential (Clock-Clock#) Measurement Points (Tperiod, Duty Cycle and Jitter)

# **Ordering Information**

| Ordering Code | Package Type                 | Operating Range           |  |

|---------------|------------------------------|---------------------------|--|

| Lead-free     |                              |                           |  |

| SL28DB200AZC  | 16-pin TSSOP                 | Commercial, 0°C to 85°C   |  |

| SL28DB200AZCT | 16-pin TSSOP—(Tape and Reel) | Commercial, 0°C to 85°C   |  |

| SL28DB200AZI  | 16-pin TSSOP                 | Industrial, -40°C to 85°C |  |

| SL28DB200AZIT | 16-pin TSSOP—(Tape and Reel) | Industrial, -40°C to 85°C |  |

Note: All oderables are Lead-free and RoHS compliant

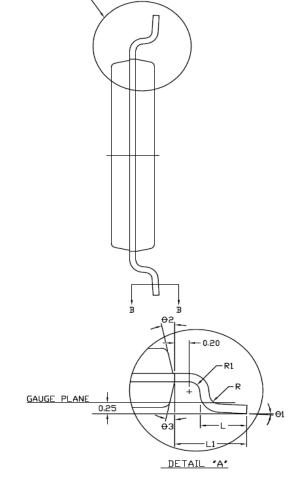

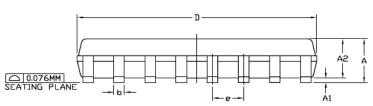

## **Package Drawing and Dimensions**

#### 16-Lead Thin Shrunk Small Outline Package

SEE DETAIL 'A'-

| SYMB□L         | DIMEN   | NDIS   | IN MM | DIMEN     | SION I | N INCH |

|----------------|---------|--------|-------|-----------|--------|--------|

| SIMBUL         | MIN.    | N□M.   | MAX.  | MIN.      | N□M.   | MAX.   |

| Α              |         |        | 1.20  |           |        | .047   |

| A1             | 0.05    |        | 0.15  | .002      |        | .006   |

| A2             | 0.80    | 0.90   | 1.05  | .031      | .035   | .041   |

| b              | 0.19    |        | 0.30  | .007      |        | .012   |

| b1             | 0.19    | 0.22   | 0.25  | .007      | .009   | .010   |

| c              | 0.09    |        | 0.20  | .004      |        | .008   |

| ⊂1             | 0.09    |        | 0.16  | .004      |        | .006   |

| D              | 4.90    | 5.00   | 5.10  | .193      | .197   | .200   |

| е              | 0.      | 65 BS  | C.    | .026 BSC  |        |        |

| E              | 6.      | 40 BS  | C.    | .252 BSC. |        |        |

| E1             | 4.30    | 4.40   | 4.50  | .169      | .173   | .177   |

| L              | 0.50    | 0.60   | 0.75  | .020      | .024   | .030   |

| ∟1             | 1.      | 00 REF | ₹.    | .039 REF. |        | ₹.     |

| R              | 0.09    |        |       | .004      |        |        |

| R1             | 0.09    |        |       | .004      |        |        |

| <del>0</del> 1 | 0       |        | 8     | 0         |        | 8      |

| 92             | 12 REF. |        |       | 12 REF.   |        |        |

| <del>0</del> 3 | 12 REF. |        |       | 1         | 2 REF  |        |

| <u> </u>    | —b— | <u> </u> |  |  |  |

|-------------|-----|----------|--|--|--|

| c           |     | ⊂1       |  |  |  |

| Ŧ           | b1  | 1        |  |  |  |

| SECTION B-B |     |          |  |  |  |

#### NDTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSION 'D' DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE.

- 3. DIMENSION 'E1' DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION, INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 PER SIDE.

- 4. "N" IS THE NUMBER OF TERMINAL POSITIONS.

- 5. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- 6. REFERENCE DRAWING JEDEC MD-153, VARIATION AB.

## **Document History Page**

| Document Title: SL28DB200 PCI Express Gen2 and SATA Differential Buffer Document #: 38-07722 Rev *C |                                                                    |          |     |                                |  |  |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------|-----|--------------------------------|--|--|

| REV.                                                                                                | REV.   ECR#   Issue Date   Orig. of Change   Description of Change |          |     |                                |  |  |

| 1.0                                                                                                 |                                                                    | 06/17/10 | TRP | Initial Release                |  |  |

| AA                                                                                                  |                                                                    | 09/27/10 | TRP | Updated Dynamic Supply Current |  |  |

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.