## **General Description**

The MAX8523 dual-phase gate driver, along with the MAX8524\*/MAX8525 multiphase controllers, provides flexible 2- to 8-phase CPU core-voltage supplies. The 0.5 $\Omega$ /0.95 $\Omega$  driver resistance allows up to 30A output current per phase.

Each MOSFET driver in the MAX8523 is capable of driving 3000pF capacitive loads with only 15ns propagation delay and 11ns typical rise and fall times, allowing operations up to 1.2MHz per phase. Adaptive dead time controls low-side MOSFET turn-on, and user-programmable dead time controls high-side MOSFET turn-on. This maximizes converter efficiency while allowing operation with a variety of MOSFETs and controller ICs. An undervoltage lockout (UVLO) circuit allows proper power-on sequencing. PWM\_ signal inputs are both TTL and CMOS compatible.

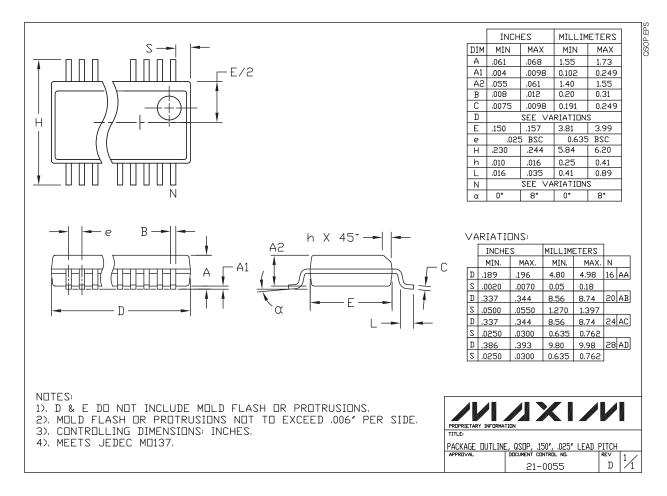

The MAX8523 is available in a space-saving 16-pin QSOP package, and specified for -40°C to +85°C operation.

### \_Applications

Core Voltage Supplies for Pentium<sup>™</sup> IV Microprocessors Servers and Workstations Desktop Computers Voltage Regulator Modules (VRMs) DC-to-DC Regulator Modules Switches, Routers, and Storage

### **Features**

- ♦ 6A Peak Gate-Drive Current

- Up to 1.2MHz Operation

- Up to 6.5V Gate-Drive Voltage

- 0.5Ω/0.95Ω Low-Side Drivers

- Capable of 30A Output per Phase

- Adaptive Shoot-Through Protection

- User-Programmable Delay Time

- TTL and CMOS Input Compatible

- UVLO for Proper Sequencing

- Flexible 2- to 8-Phase Implementation with MAX8524 and MAX8525

- Space-Saving (4.9mm × 6mm) 16-Pin QSOP Package

### **Ordering Information**

| PART |            | TEMP RANGE     | PIN-PACKAGE |  |

|------|------------|----------------|-------------|--|

|      | MAX8523EEE | -40°C to +85°C | 16 QSOP     |  |

\*Future product. Contact factory for availability.

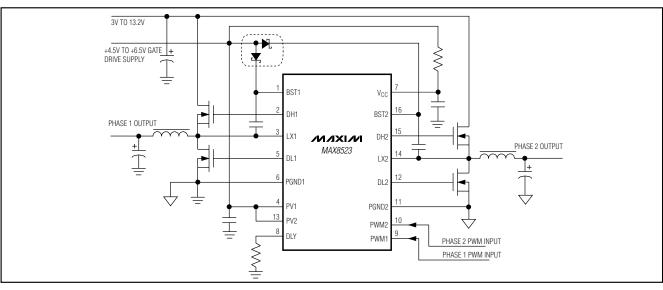

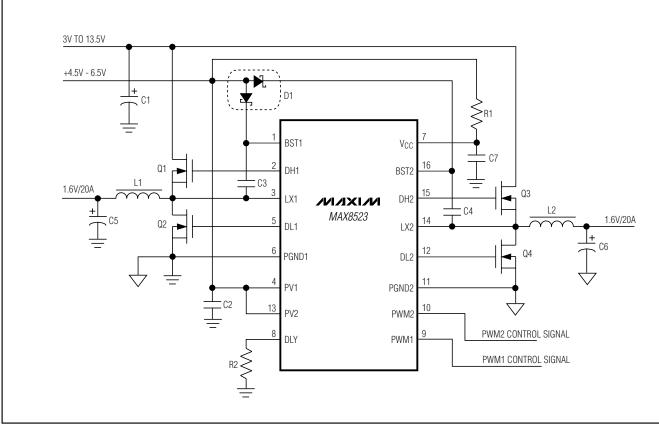

## **Typical Operating Circuit**

Pentium is a trademark of Intel Corp.

####

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| BST_ to PGND             | 0.3V to +26V                     |

|--------------------------|----------------------------------|

| LX_to PGND               | 1V to +14V                       |

| DH_ to PGND              | 0.3V to (BST_ + 0.3V)            |

| DH_ to LX                | 0.3V to +7V                      |

| BST_ to LX               | 0.3V to +7V                      |

| DL_ to PGND              | 0.3V to (PV_ + 0.3V)             |

| PV_ to PGND              | 0.3V to +7V                      |

| PGND2 to PGND1           | 0.3V to +0.3V                    |

| V <sub>CC</sub> to PGND1 | 0.3V to +7V                      |

| DLY to PGND1             | 0.3V to (V <sub>CC</sub> + 0.3V) |

| PWM_ to PGND10.                                       | .3V to (PV2 + 0.3V) |

|-------------------------------------------------------|---------------------|

| V <sub>CC</sub> to PV1                                | 7V to +0.3V         |

| DH_, DL_ Continuous Current                           | ±200mA              |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                     |

| 16-Pin QSOP (derate 8.3mW/°C above +70°               | °C)667mW            |

| Operating Temperature Range                           | 40°C to +85°C       |

| Junction Temperature                                  | +150°C              |

| Storage Temperature Range                             |                     |

| Lead Temperature (soldering, 10s)                     | +300°C              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{VCC} = V_{PV1} = V_{PV2} = V_{BST1} = V_{DST2} = V_{DLY} = 5V$ ,  $V_{PGND1} = V_{PGND2} = V_{LX1} = V_{LX2} = 0V$ ; **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                                                   | CONDITIONS                                    | MIN  | ТҮР  | MAX  | UNITS |

|-----------------------------------------------------------------------------|-----------------------------------------------|------|------|------|-------|

| UNDERVOLTAGE PROTECT                                                        | ION                                           | ·    |      |      | •     |

| Supply Voltage Range                                                        |                                               | 4.5  |      | 6.5  | V     |

| UVLO                                                                        | V <sub>CC</sub> rising                        | 3.25 | 3.5  | 3.8  | V     |

| UVLO                                                                        | V <sub>CC</sub> falling                       | 3.0  |      | 3.5  |       |

| luce                                                                        | $DLY = V_{CC}$                                |      | 50   | 100  | μΑ    |

| IVCC                                                                        | Dynamic, $R_{DLY} = 50k\Omega$                |      | 0.5  | 1    | mA    |

| I                                                                           | PWM_ = GND                                    |      | 1    | 10   | μA    |

| IPV_                                                                        | $PWM_{=}V_{CC}$                               |      | 1.2  | 2    | mA    |

| l                                                                           | PWM_ = GND                                    |      | 0.1  | 10   | μA    |

| IBST_                                                                       | $PWM_{=}V_{CC}$                               |      | 1.2  | 2    | mA    |

| I <sub>BST1</sub> + I <sub>PV1</sub> + I <sub>BST2</sub> + I <sub>PV2</sub> | 250kHz                                        |      | 4    | 8    | mA    |

| DRIVER SPECIFICATIONS                                                       |                                               |      |      |      |       |

| DLL Driver Desistence                                                       | $PWM_ = PGND1, V_{BST} = 4.5V$                |      | 0.65 | 1.2  | Ω     |

| DH_ Driver Resistance                                                       | $PWM_{=} V_{CC}, V_{BST_{=}} = 4.5V$          |      | 0.8  | 1.35 |       |

|                                                                             | $PWM_ = PGND1, V_{PV_} = 4.5V$                |      | 0.95 | 1.6  | Ω     |

| DL_ Driver Resistance                                                       | $PWM_{=} V_{CC}, V_{PV} = 4.5V$               |      | 0.5  | 0.9  |       |

| DH_ Rise Time                                                               | $PWM_ = V_{CC}, V_{BST} = 5V, 3nF load$       |      | 11   |      | ns    |

| DH_ Fall Time                                                               | PWM_ = PGND1, V <sub>BST</sub> = 5V, 3nF load |      | 9.5  |      | ns    |

| DL_ Rise Time                                                               | $PWM_ = V_{CC}, V_{PV} = 5V, 3nF load$        |      | 8.5  |      | ns    |

| DL_Fall Time                                                                | PWM_ = PGND1, V <sub>PV</sub> = 5V, 3nF load  |      | 6.5  |      | ns    |

| DH_ Propagation Delay                                                       | PWM_falling, $V_{BST} = 5V$                   |      | 15   |      | ns    |

| DL_ Propagation Delay                                                       | PWM_rising, $V_{BST} = 5V$                    |      | 8    |      | ns    |

| PWM_ INPUT                                                                  |                                               |      |      |      |       |

| Input Current                                                               | $V_{PWM} = 0V \text{ or } 6.5V$               |      | 0.01 | 1    | μA    |

| Input Voltage High                                                          |                                               | 2.5  |      |      | V     |

| Input Voltage Low                                                           |                                               |      |      | 0.8  | V     |

## **ELECTRICAL CHARACTERISTICS**

$(V_{VCC} = V_{PV1} = V_{PV2} = V_{BST1} = V_{BST2} = 5V, V_{PGND1} = V_{PGND2} = V_{LX1} = V_{LX2} = 0V; T_A = -40^{\circ}C \text{ to } +85^{\circ}C, unless otherwise noted.)$ (Note 1)

| PARAMETER                                 | CONDITIONS                            | MIN  | ТҮР | MAX  | UNITS |  |

|-------------------------------------------|---------------------------------------|------|-----|------|-------|--|

| UNDERVOLTAGE PROTECTION                   | ON                                    | ·    |     |      | -     |  |

| Supply Voltage Range                      |                                       | 4.5  |     | 6.5  | V     |  |

| UVLO                                      | V <sub>CC</sub> rising                | 3.25 |     | 3.8  | V     |  |

| UVLO                                      | V <sub>CC</sub> falling               | 3.0  |     | 3.5  | v     |  |

| huoo                                      | $DLY = V_{CC}$                        |      |     | 100  | μA    |  |

| IVCC                                      | Dynamic, $R_{DLY} = 50k\Omega$        |      |     | 1    | mA    |  |

|                                           | PWM_ = GND                            |      |     | 10   | μA    |  |

| IPV_                                      | $PWM_{=} V_{CC}$                      |      |     | 2    | mA    |  |

| 1997                                      | PWM_ = GND                            |      |     | 10   | μA    |  |

| I <sub>BST_</sub>                         | $PWM_{=} V_{CC}$                      |      |     | 2    | mA    |  |

| $I_{BST1} + I_{PV1} + I_{BST2} + I_{PV2}$ | 250kHz                                |      |     | 8    | mA    |  |

| DRIVER SPECIFICATIONS                     |                                       |      |     |      |       |  |

|                                           | $PWM_ = PGND1, V_{BST_} = 4.5V$       |      |     | 1.2  | Ω     |  |

| DH_ Driver Resistance                     | $PWM_ = V_{CC}, V_{BST_} = 4.5V$      |      |     | 1.35 |       |  |

| DI Driver Registeres                      | $PWM_ = PGND1, V_{PV_} = 4.5V$        |      |     | 1.6  |       |  |

| DL_ Driver Resistance                     | $PWM_{-} = V_{CC}, V_{PV_{-}} = 4.5V$ |      |     | 0.9  | Ω     |  |

| PWM_INPUT                                 |                                       |      |     |      |       |  |

| Input Current                             | $V_{PWM} = 0V \text{ or } 6.5V$       |      |     | 1    | μA    |  |

| Input Voltage High                        |                                       | 2.5  |     |      | V     |  |

| Input Voltage Low                         |                                       |      |     | 0.8  | V     |  |

Note 1: Specifications at -40°C guaranteed by design.

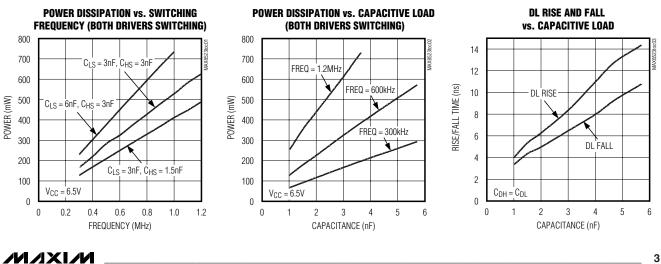

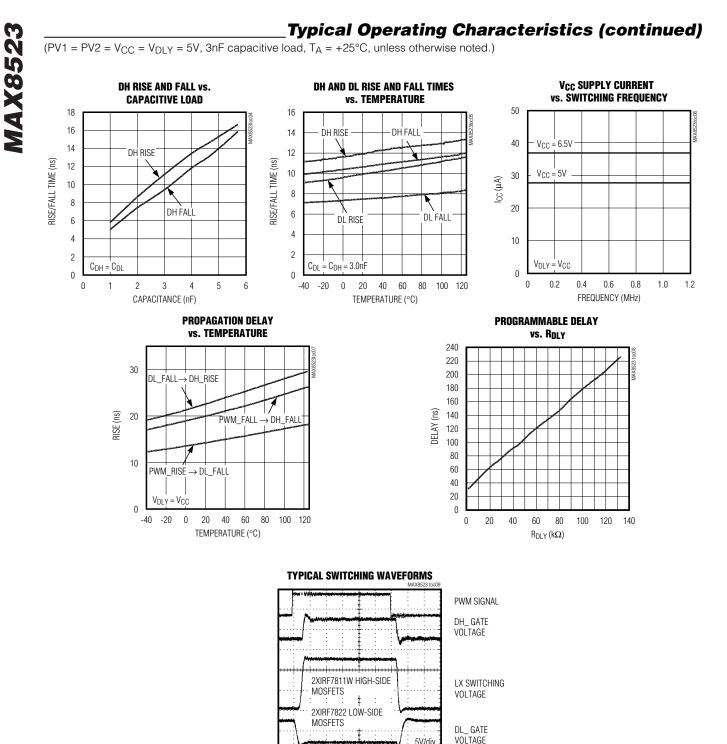

## **Typical Operating Characteristics**

(PV1 = PV2 =  $V_{CC}$  =  $V_{DLY}$  = 5V, 3nF capacitive load, T<sub>A</sub> = +25°C, unless otherwise noted.)

100 ns

5V/div

## Pin Description

| PIN                                                                                                      | NAME | FUNCTION                                                                                                                              |

|----------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                        | BST1 | Boost Flying Capacitor Connection, Phase 1. Connect a 0.22µF or higher ceramic capacitor between BST1 and LX1.                        |

| 2                                                                                                        | DH1  | High-Side Gate-Driver Output, Phase 1                                                                                                 |

| 3 LX1 Switching Node (Inductor) Connection, Phase 1                                                      |      | Switching Node (Inductor) Connection, Phase 1                                                                                         |

| 4                                                                                                        | PV1  | Gate-Drive Supply for DL1. Bypass to PGND1 with a 2.2 $\mu$ F or higher capacitor. Connect PV1 and PV2 together.                      |

| 5                                                                                                        | DL1  | Low-Side Gate-Driver Output, Phase 1                                                                                                  |

| 6 PGND1 Power Ground for DL1. Connect PGND1 and PGND2 together. Internal analog ground is conn<br>PGND1. |      | Power Ground for DL1. Connect PGND1 and PGND2 together. Internal analog ground is connected to PGND1.                                 |

| 7 V <sub>CC</sub> Supply Voltage. Bypass V <sub>CC</sub> to PGND1 with a 0.1µF (min) capacitor.          |      | Supply Voltage. Bypass V <sub>CC</sub> to PGND1 with a 0.1µF (min) capacitor.                                                         |

| 8                                                                                                        | DLY  | Connect a resistor from DLY to PGND1 to set dead time between DL_ falling and DH_ rising. Connect to $V_{CC}$ for default 20ns delay. |

| 9 PWM1 Phase 1 PWM Logic Input. DH1 is high when PW                                                      |      | Phase 1 PWM Logic Input. DH1 is high when PWM1 is high; DL1 is high when PWM1 is low.                                                 |

|                                                                                                          |      | Phase 2 PWM Logic Input. DH2 is high when PWM2 is high; DL2 is high when PWM2 is low.                                                 |

| 11 PGND2 Power Ground for DL2                                                                            |      | Power Ground for DL2                                                                                                                  |

| 12                                                                                                       | DL2  | Low-Side Gate-Driver Output, Phase 2                                                                                                  |

| 13                                                                                                       | PV2  | Gate-Drive Supply for DL2. Bypass to PGND2 with a 2.2 $\mu$ F or higher capacitor. Connect PV1 and PV2 together.                      |

| 14                                                                                                       | LX2  | Switching Node (Inductor) Connection, Phase 2                                                                                         |

| 15                                                                                                       | DH2  | High-Side Gate-Driver Output, Phase 2                                                                                                 |

| 16                                                                                                       | BST2 | Boost Flying Capacitor Connection, Phase 2. Connect a $0.22\mu$ F or higher ceramic capacitor between BST2 and LX2.                   |

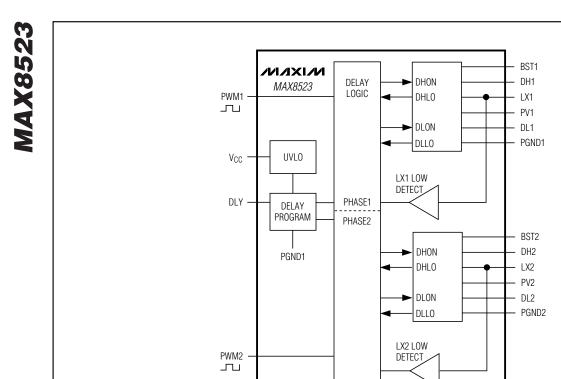

## **Detailed Description**

The MAX8523 dual-phase gate driver, along with the MAX8524/MAX8525 multiphase controllers, provides flexible 2- to 8-phase CPU core-voltage supplies. The 0.5 $\Omega$ /0.95 $\Omega$  driver resistance allows up to 30A output current per phase.

Each MOSFET driver in the MAX8523 is capable of driving 3000pF capacitive loads with only 15ns propagation delay and 11ns typical rise and fall times, allowing operations up to 1.2MHz per phase. Adaptive dead time controls low-side MOSFET turn-on, and user-programmable dead time controls high-side MOSFET turn-on. This maximizes converter efficiency, while allowing operation with a variety of MOSFETs and PWM controller ICs. A UVLO circuit allows proper power-on sequencing. PWM\_ signal inputs are both TTL and CMOS compatible.

### **Principle of Operation**

#### MOSFET Gate Drivers (DH\_, DL\_)

The high-side drivers (DH\_) have typical  $0.8\Omega$  sourcing resistance and  $0.65\Omega$  sinking resistance, resulting in 6A peak sourcing current and 7A peak sinking current with 5V supply voltage. The low-side drivers (DL\_) have typical  $0.95\Omega$  sourcing resistance and  $0.5\Omega$  sinking resistance, yielding 5A peak sourcing current and 10A peak sinking current. This reduces switching losses, making the MAX8523 ideal for both high-frequency and high-output-current applications.

#### Shoot-Through Protection

Adaptive shoot-through protection is incorporated for the switching transition after the high-side MOSFET is turned off and before the low-side MOSFET is turned on. The low-side driver is turned on only when the LX voltage falls below 1.8V. Furthermore, the delay time between the low-side MOSFET turn-off and high-side MOSFET turn-on can be adjusted by selecting the value of R2 (see the *R<sub>DLY</sub> Selection* section).

M/X/M

Figure 1. MAX8523 Functional Diagram

#### **Undervoltage Lockout (UVLO)**

When V<sub>CC</sub> is below the UVLO threshold (3.5V typ), DH\_ and DL\_ are held low. Once V<sub>CC</sub> is above the UVLO threshold and PWM\_ is low, DL\_ is kept high and DH\_ is kept low. This prevents output from rising before a valid PWM signal is applied.

#### Vcc Decoupling

V<sub>CC</sub> provides the supply voltage for the internal logical circuit. To avoid malfunctions due to the switching noise on the DH\_, DL\_, and LX\_ pins, RC decoupling is recommended for the V<sub>CC</sub> pin. Place a  $10\Omega$  resistor (R1) from the supply voltage to the V<sub>CC</sub> pin and a  $0.1\mu$ F (C7) capacitor from the V<sub>CC</sub> pin to PGND1.

#### **Boost Capacitor Selection**

The MAX8523 uses a bootstrap circuit to generate the floating supply voltages for the high-side drivers (DH\_). The selected high-side MOSFET determines appropriate boost capacitance values, according to the following equation:

$$C_{BST} = \frac{Q_{GATE}}{\Delta V_{BST}}$$

where  $Q_{GATE}$  is the total gate charge of the high-side MOSFET and  $\Delta V_{BST}$  is the voltage variation allowed on the high-side MOSFET drive. Choose  $\Delta V_{BST}$  = 0.1V to 0.2V when determining the CBST. Low-ESR ceramic capacitors should be used for C\_3 and C\_4.

Figure 2. Typical Application Circuit

#### **PV\_ Decoupling**

PV\_ provides the supply voltages for the low-side drivers (DL\_). The decoupling capacitors at PV\_ also charge the BST capacitors during the time period when DL\_ is high. Therefore, the decoupling capacitor C2 for PV\_ should be large enough to minimize the ripple voltage during switching transitions. C2 should be chosen according to the following equation:

$$C2 = 10 \times C_{BST}$$

#### **RDLY Selection**

Connect DLY to V<sub>CC</sub> for the default delay time, typically 20ns. Add a delay resistor, R<sub>DLY</sub>, between DLY and PGND1 to increase the delay between the low-side MOSFET drive turn-off and the high-side MOSFET turnon. See the *Typical Operating Characteristics* to select R<sub>DLY</sub>.

#### Avoiding dV/dt-Induced Low-Side MOSFET Turn-On

At high input voltages, fast turn-on of the high-side MOSFET could momentarily turn on the low-side MOSFET due to the high dV/dt appearing at the drain of the low-side MOSFET. The high dV/dt causes a current flow through the Miller capacitance (C<sub>RSS</sub>) and the input capacitance (C<sub>ISS</sub>) of the low-side MOSFET. Improper selection of the low-side MOSFET that has a high ratio of C<sub>RSS</sub>/C<sub>ISS</sub> makes the problem more severe. To avoid the problem, give special attention to the ratio of C<sub>RSS</sub>/C<sub>ISS</sub> when selecting the low-side MOSFET. Adding a resistor between the BST and the C<sub>BST</sub> can slow the high-side MOSFET turn-on. Similarly, adding a capacitor from the gate to the source of the high-side MOSFET has the same effect. However, both methods are at the expense of increasing the switching losses.

7

**MAX8523**

## Table 1. Typical Component Values (250kHz Operation, 20A/Phase Output Current)

| COMPONENT | DESCRIPTION                                                                       | PART NUMBER                         |

|-----------|-----------------------------------------------------------------------------------|-------------------------------------|

| C1        | 5 x 330µF/25V, 23m $\Omega$ (max) ESR input filtering capacitor                   | Sanyo 25MV330WX                     |

| C2        | 2.2µF/10V ceramic capacitor                                                       | Taiyo Yuden JMK107BJ225MA           |

| C3, C4    | 0.22µF/10V ceramic capacitors                                                     | Taiyo Yuden GMK212BJ224MG           |

| C5, C6    | $3 \times 820 \mu$ F/4V, $12m\Omega$ (max) ESR electrolytic capacitors            | Sanyo 4SP820M                       |

| C7        | 0.1µF/10V ceramic capacitor                                                       | Taiyo Yuden UMK212BJ104MG           |

| D1        | Dual Schottky diode                                                               | Central Semiconductor CMPSH-3A      |

| L1, L2    | 0.66µH/29A, 2.1m $\Omega$ (typ),<br>2.5m $\Omega$ (max) R <sub>DC</sub> inductors | Sumida CDEP134-H                    |

| Q1, Q2    | High-side MOSFETs                                                                 | Siliconix SUB70N03-09BP             |

| Q3, Q4    | Low-side MOSFETs                                                                  | Fairchild FDB7045L                  |

| R1        | $10\Omega \pm 5\%$ resistor (0603)                                                | V <sub>CC</sub> decoupling resistor |

| R2        | $2k\Omega$ to $125k\Omega$ ±1% dead-time delay programming resistor (0603)        | —                                   |

Table 2. Typical Component Values (800kHz Operation, 20A/Phase Output Current)

| COMPONENT | DESCRIPTION                                                                      | PART NUMBER                         |

|-----------|----------------------------------------------------------------------------------|-------------------------------------|

| C1        | $5 \times 10 \mu$ F/25V, $10 m\Omega$ (max) ESR input filtering capacitor (1812) | Taiyo Yuden TMK432BJ106MM           |

| C2        | 2.2µF/10V ceramic capacitor                                                      | Taiyo Yuden JMK107BJ225MA           |

| C3, C4    | 0.22µF/10V ceramic capacitors                                                    | Taiyo Yuden GMK212BJ224MG           |

| C5, C6    | $3 \times 680 \mu$ F/2V, 5m $\Omega$ (max) ESR SP capacitors                     | Sanyo 2RSTPD680M5                   |

| C7        | 0.1µF/10V ceramic capacitor                                                      | Taiyo Yuden UMK212BJ104MG           |

| D1        | Dual Schottky diode                                                              | Central Semiconductor CMPSH-3A      |

| L1, L2    | 0.23 $\mu$ H/30A, 1.1m $\Omega$ (max) R <sub>DC</sub> inductors                  | TDK SPM12535T-R23M300               |

| Q1, Q2    | High-side MOSFETs                                                                | IR IRF7801                          |

| Q3, Q4    | Low-side MOSFETs                                                                 | IR 2XIRF7822                        |

| R1        | $10\Omega \pm 5\%$ resistor (0603)                                               | V <sub>CC</sub> decoupling resistor |

| R2        | $2k\Omega$ to $125k\Omega \pm 1\%$ dead-time delay programming resistor (0603)   | _                                   |

### **Applications Information**

#### **Power Dissipation**

Power dissipation in the IC package comes mainly from switching the MOSFETs. Therefore, it is a function of both switching frequency and the total gate charge of the selected MOSFETs. The total power dissipation when both drivers are switching is given by:

$$P_{IC} = 2 \times f_{S} \times (N \times Q_{G_{TOTAL}HS} \times \frac{R_{HS}}{R_{HS} + (R_{G_{HS}}/N)} + M \times Q_{G_{TOTAL}LS} \times \frac{R_{LS}}{R_{LS} + (R_{G_{LS}}/M)} \times V_{PV_{L}} + V_{VCC} \times I_{VCC}$$

where fs is the switching frequency, QG\_TOTAL\_HS is the total gate charge of the selected high-side MOSFET, QG\_TOTAL\_LS is the total gate charge of the selected low-side MOSFET, N is the total number of the high-side MOSFETs in parallel, M is the total number of the low-side MOSFETs in parallel, VPV\_ is the voltage at the PV\_ pin, RHs is the on-resistance of the high-side driver, RLs is the on-resistance of the low-side driver, RG\_HS is the gate resistance of the selected high-side MOSFET, RG\_LS is the gate resistance of the selected low-side MOSFETs, VVCC is the voltage at the VCC pin, and IVCC is the supply current at the VCC pin.

#### TOP VIEW BST1 16 BST2 2 5 DH2 DH1 LX1 14 LX2 3 MIXIM PV2 PV1 MAX8523 13 4 DL1 12 DL2 5 PGND1 6 PGND2 Vcc 10 PWM2 7 DLY 8 9 PWM1 QSOP

### **Pin Configuration**

#### **PC Board Layout Considerations**

The MAX8523 MOSFET driver sources and sinks large currents to drive MOSFETs at high switching speeds. The high di/dt can cause unacceptable ringing if the trace lengths and impedances are not well controlled. The following PC board layout guidelines are recommended when designing with the MAX8523:

- 1) Place all decoupling capacitors (C2, C3, C4, C7) as close to their respective pins as possible.

- Minimize the high-current loops from the input capacitor, upper-switching MOSFET, and low-side MOSFET back to the input capacitor negative terminal.

- Provide enough copper area at and around the switching MOSFETs and inductors to aid in thermal dissipation.

- Connect the PGND1 and PGND2 pins of the MAX8523 as close as possible to the source of the low-side MOSFETs.

- 5) Keep LX1 and LX2 away from sensitive analog components and nodes. Place the IC and analog components on the opposite side of the board from the power-switching node if possible.

### **Chip Information**

TRANSISTOR COUNT: 1187 PROCESS: BICMOS

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <u>www.maxim-ic.com/packages</u>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

MAX8523

\_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2003 Maxim Integrated Products

Printed USA

A maxim is a registered trademark of Maxim Integrated Products.