## 0.3A/0.6A, High/Low-Side MOSFET Driver

### **General Description**

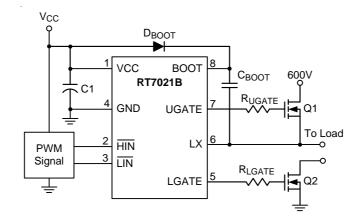

The RT7021A/B is a high-voltage gate driver IC with dual outputs. The IC, together with an external bootstrap network, drives dual n-channel MOSFETs or IGBTs with input voltage rail up to 600V.

The IC is equipped with a "common-mode dV/dt noise canceling technique" to provide high dV/dt immunity which enables stable operation under high dV/dt noise circumstances. Two Under-Voltage Lockout (UVLO) functions continuously monitor the bias voltages on VCC and BOOT-to-LX for preventing malfunction when the bias voltages are lower than the specified threshold voltages. The logic level of the PWM signal input pins are compatible with standard TTL logic level for ease of interfacing with controlling devices.

### **Applications**

- PDP Scan Driver

- Fluorescent Lamp Ballast

- SMPS

- Motor Driver

#### **Features**

- Floating Channels Designed for Bootstrap Operation with Input Voltage up to 600V

- 300mA/600mA Sourcing/Sinking Current

- High dV/dt Immunity: ±50V/nsec

- V<sub>CC</sub> and V<sub>BOOT-LX</sub> Supply Range from 13V to 20V

- Under-Voltage Lockout Functions for Both Channels

- TTL Compatible Logic Input

- Matched Propagation Delay below 20ns

- Outputs in Phase with Input (RT7021A) or Out of Phase with Input (RT7021B)

- RoHS Compliant and Halogen Free

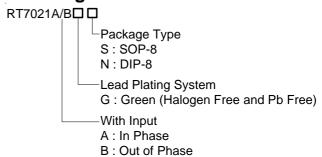

### **Ordering Information**

#### Note:

#### Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

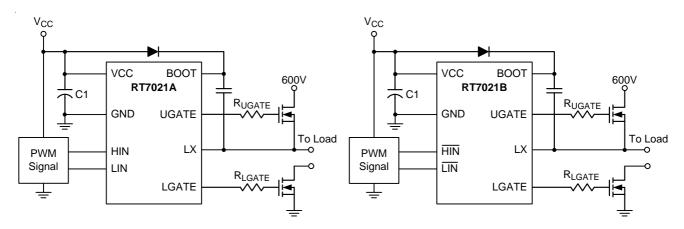

## **Simplified Application Circuit**

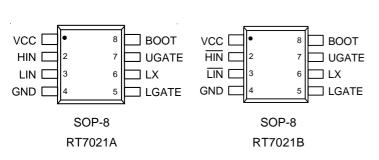

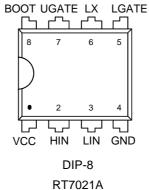

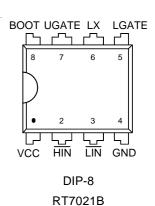

## Pin Configuration

#### (TOP VIEW)

### **Marking Information**

RT7021AGS

RT7021A **GSYMDNN**  RT7021AGS: Product Number

YMDNN: Date Code

RT7021BGS

RT7021B **GSYMDNN**  RT7021BGS: Product Number

YMDNN: Date Code

RT7021AGN

RichTek RT7021A **GNYMDNN**  RT7021AGN: Product Number

YMDNN: Date Code

RT7021BGN

RichTek RT7021B **GNYMDNN**  RT7021BGN: Product Number

YMDNN: Date Code

## **Functional Pin Description**

| Pin No.                                          |       | Din Nome                                 | Din Frantian                                |  |

|--------------------------------------------------|-------|------------------------------------------|---------------------------------------------|--|

| SOP-8                                            | DIP-8 | Pin Name                                 | Pin Function                                |  |

| 1                                                | 1     | VCC                                      | Supply voltage input.                       |  |

|                                                  | 2     | HIN (RT7021A)                            | Logic input for high-side gate driver.      |  |

| 2                                                |       | HIN (RT7021B)                            | Logic input for high-side gate driver.      |  |

|                                                  | 3     | LIN (RT7021A)                            | Logic input for low-side gate driver.       |  |

| 3                                                |       | LIN (RT7021B)                            | Logic input for low-side gate driver.       |  |

| 4 4 GND Logic ground and low-side driver return. |       | Logic ground and low-side driver return. |                                             |  |

| 5 5 LGATE Low-side driver output.                |       | Low-side driver output.                  |                                             |  |

| 6                                                | 6     | LX                                       | LX Return for high-side gate driver.        |  |

| 7                                                | 7     | UGATE                                    | High-side driver output.                    |  |

| 8                                                | 8     | воот                                     | Bootstrap supply for high-side gate driver. |  |

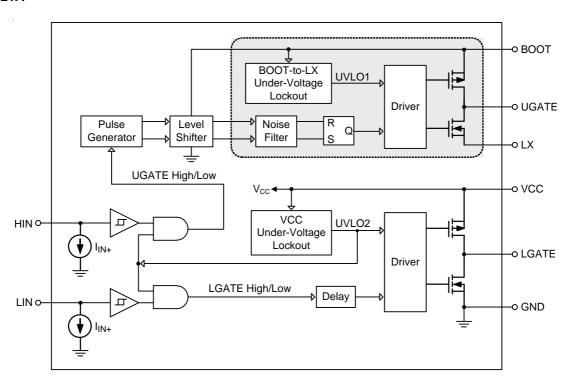

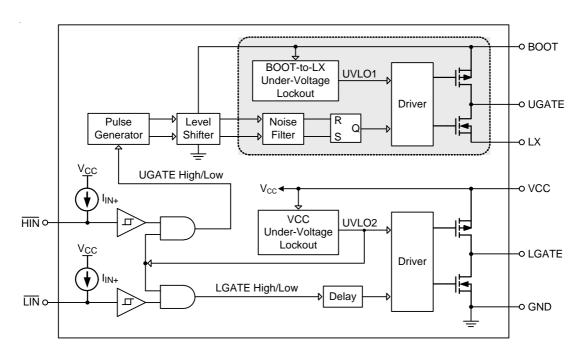

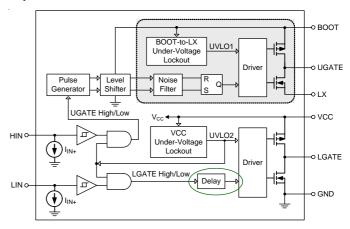

## **Functional Block Diagram**

#### For RT7021A

#### For RT7021B

## **Operation**

The RT7021A/B is a high-voltage gate driver for driving high-side and low-side MOSFETs. The RT7021A/B uses ultra high voltage device and floating well to allowed UGATE to drive external MOSFET operating up to 600V. When the HIN voltage is above the logic-high threshold, the UGATE voltage goes high to turn on the external MOSFET. When the HIN voltage is below the logic-low threshold, the MOSFET is turned off. The operating behavior of the LGATE, controlled by the LIN pin, is like the behavior of the UGATE.

#### **Under-Voltage Lockout (UVLO) Function**

When the VCC or BOOT-to-LX voltage is lower the UVLO threshold, the UGATE and LGATE output will be disabled.

#### **Pulse Generator**

The pulse generator is used to transmit the HIN input signal to the UGATE driver.

www.richtek.com

## **Absolute Maximum Ratings** (Note 1)

| • VCC Supply Voltage, V <sub>CC</sub>                                       | 0.3V to 25V                     |

|-----------------------------------------------------------------------------|---------------------------------|

| • LX to GND                                                                 | 0.3V to 625V                    |

| • BOOT to LX, V <sub>BOOT-LX</sub>                                          | 0.3V to 25V                     |

| • UGATE to LX                                                               | $-0.3V$ to $V_{BOOT-LX} + 0.3V$ |

| • LGATE to GND                                                              | $-0.3V$ to $V_{CC} + 0.3V$      |

| • HIN, LIN, HIN, LIN to GND                                                 | $-0.3V$ to $V_{CC} + 0.3V$      |

| Allowable LX Voltage Slew Rate, dV <sub>LX</sub> /dt                        | 50V/ns to 50V/ns                |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                                 |

| SOP-8                                                                       | - 0.53W                         |

| DIP-8                                                                       | - 0.74W                         |

| Package Thermal Resistance (Note 2)                                         |                                 |

| SOP-8, $\theta_{JA}$                                                        | - 188°C/W                       |

| DIP-8, $\theta_{JA}$                                                        | - 134.9°C/W                     |

| Junction Temperature                                                        | - 150°C                         |

| • Lead Temperature (Soldering, 10 sec.)                                     | - 260°C                         |

| Storage Temperature Range                                                   | 65°C to 150°C                   |

| Recommended Operating Conditions (Note 3)                                   |                                 |

| VCC Supply Voltage, V <sub>CC</sub>                                         | - 13V to 20V                    |

| • LX to GND                                                                 | 5V to 600V                      |

| • BOOT-to-LX, V <sub>BOOT-LX</sub>                                          | - 13V to 20V                    |

| • UGATE to LX                                                               | $-5V$ to $V_{BOOT-LX}$          |

|                                                                             |                                 |

#### **Electrical Characteristics**

( $V_{CC} = V_{BOOT-LX} = 15V$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Parameter                                                       | Symbol                  | Test Conditions | Min | Тур  | Max | Unit |

|-----------------------------------------------------------------|-------------------------|-----------------|-----|------|-----|------|

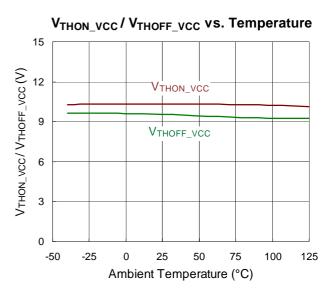

| V <sub>CC</sub> Under-Voltage Lockout<br>Threshold (On)         | V <sub>THON_VCC</sub>   |                 | 9   | 10.5 | 12  | V    |

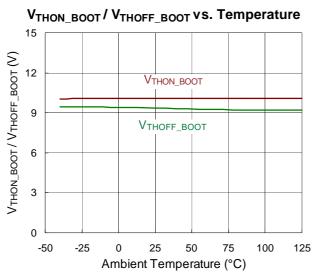

| V <sub>BOOT – LX</sub> Under-Voltage<br>Lockout Threshold (On)  | V <sub>THON_BOOT</sub>  |                 | 9   | 10.5 | 12  | ٧    |

| V <sub>CC</sub> Under-Voltage Lockout<br>Threshold (Off)        | V <sub>THOFF_</sub> vcc |                 | 8   | 9.5  | 11  | ٧    |

| V <sub>BOOT - LX</sub> Under-Voltage<br>Lockout Threshold (Off) | V <sub>THOFF_BOOT</sub> |                 | 8   | 9.5  | 11  | V    |

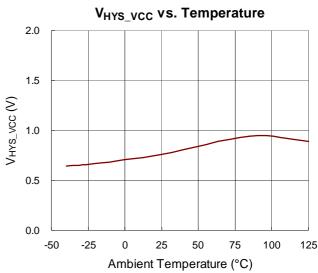

| V <sub>CC</sub> Under-Voltage Lockout<br>Hysteresis             | V <sub>HYS_</sub> VCC   |                 | -   | 1    | 1   | V    |

• LGATE to GND ------ 0 to V<sub>CC</sub>

• HIN, LIN, HIN, LIN to GND ----- 0 to V<sub>CC</sub>

• Ambient Temperature Range ----- -40°C to 125°C

| Paramet                                                    | er           | Symbol                | Test Conditions                                                                                                                                                      |  | Тур | Max | Unit |

|------------------------------------------------------------|--------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----|-----|------|

| V <sub>BOOT – LX</sub> Under-Voltage<br>Lockout Hysteresis |              | V <sub>HSY_BOOT</sub> |                                                                                                                                                                      |  | 1   |     | V    |

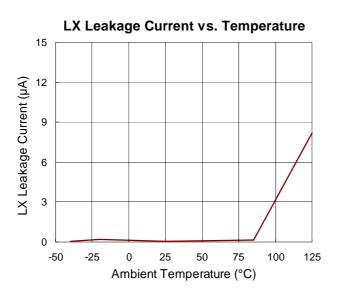

| LX Leakage Curren                                          | t            | I <sub>LK</sub>       | $V_{BOOT} = V_{LX} = 600V$                                                                                                                                           |  |     | 50  | μА   |

| VCC Quiescent Current                                      |              | IQ_VCC                |                                                                                                                                                                      |  | 220 | 400 | μА   |

| BOOT-to-LX Quieso                                          | cent Current | IQ_BOOT - LX          |                                                                                                                                                                      |  | 100 | 200 | μА   |

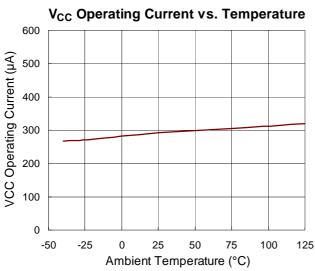

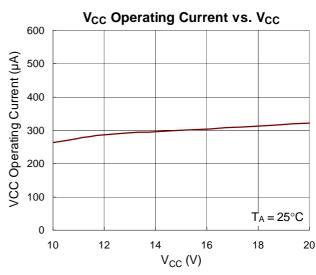

| VCC Operating Cur                                          | rent         | I <sub>P_VCC</sub>    | f = 20kHz,<br>UGATE = LGATE = Open                                                                                                                                   |  |     | 600 | μА   |

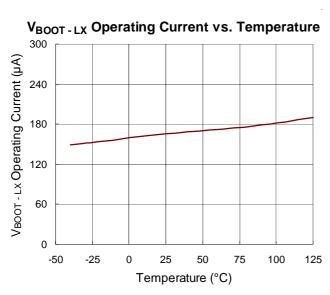

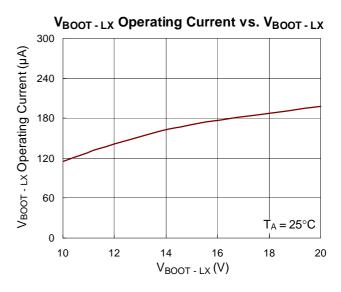

| BOOT-to-LX Opera                                           | ting Current | IP_BOOT - LX          |                                                                                                                                                                      |  |     | 600 | μА   |

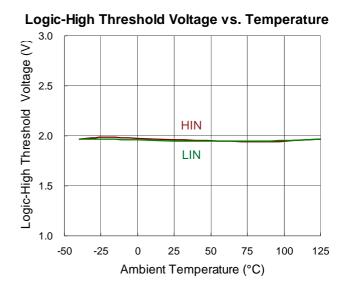

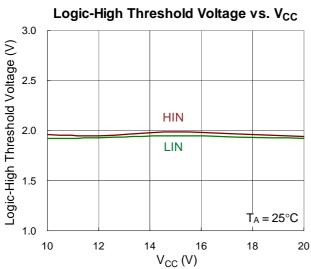

| HIN, LIN, HIN,                                             | Logic-High   | V <sub>IH</sub>       |                                                                                                                                                                      |  |     |     | V    |

| LIN Input Voltage                                          | Logic-Low    | V <sub>IL</sub>       |                                                                                                                                                                      |  |     | 0.8 |      |

| UGATE, LGATE                                               | High-Level   | Voн                   | Sourcing Current = 2mA,  VBOOT - VLGATE, VCC - VLGATE  Sourcing Current = 2mA,  VUGATE - LX, VLGATE                                                                  |  | 50  | 200 | m\/  |

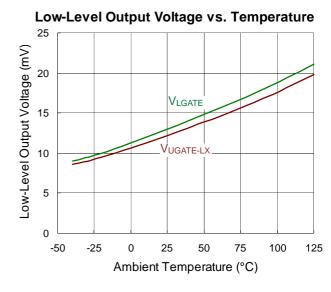

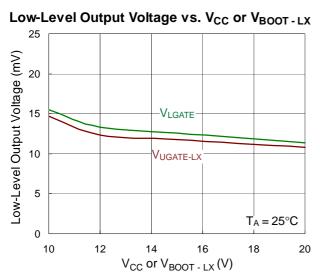

| Output Voltage                                             | Low-Level    | VoL                   |                                                                                                                                                                      |  | 20  | 100 | mV   |

| HIN, LIN Input                                             | Logic-High   | I <sub>IN+</sub>      | HIN = LIN = V <sub>CC</sub> (RT7021A)<br>HIN = LIN = 0V (RT7021A)                                                                                                    |  | 2   | 10  | ^    |

| Current                                                    | Logic-Low    | I <sub>IN</sub> _     |                                                                                                                                                                      |  |     |     | μΑ   |

| HIN, LIN Input                                             | Logic-High   | I <sub>IN</sub> _     | $\overline{\text{HIN}} = \overline{\text{LIN}} = \text{V}_{\text{CC}} (\text{RT7021B})$ $\overline{\text{HIN}} = \overline{\text{LIN}} = \text{OV} (\text{RT7021B})$ |  |     |     | _    |

| Current                                                    | Logic-Low    | I <sub>IN+</sub>      |                                                                                                                                                                      |  | 2   | 10  | μΑ   |

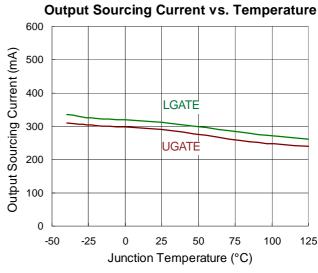

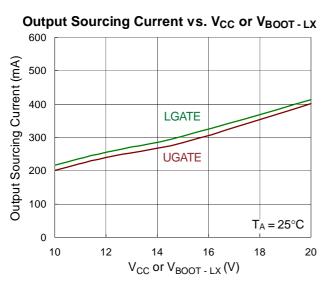

| UGATE and LGATE Sourcing Current                           |              | I <sub>O+</sub>       | UGATE = LX, LGATE = GND, Current pulse width < 10μs, Low duty                                                                                                        |  | 290 |     | mA   |

| UGATE and LGATE Sinking Current                            |              | I <sub>O</sub> _      | UGATE = BOOT, LGATE = VCC,<br>Current pulse width < 10μs, Low duty                                                                                                   |  | 600 |     | mA   |

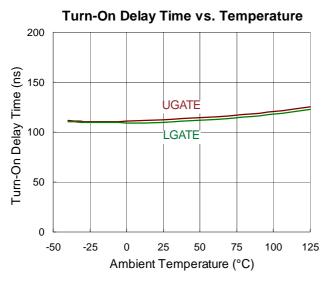

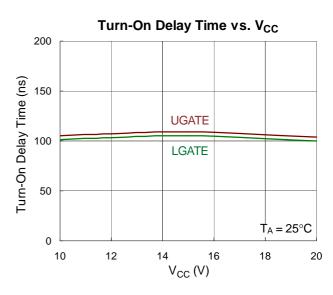

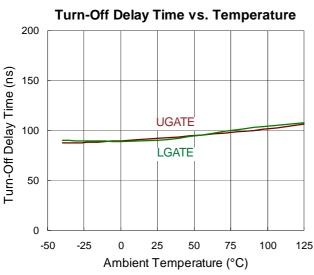

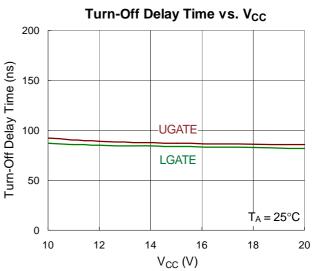

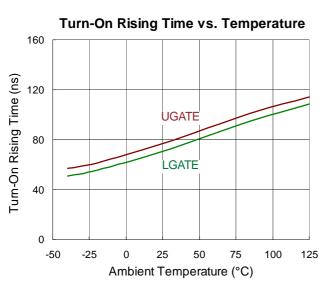

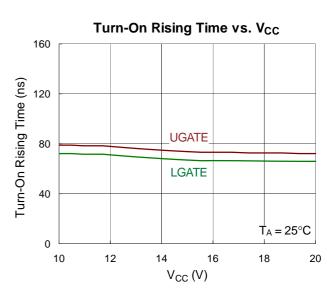

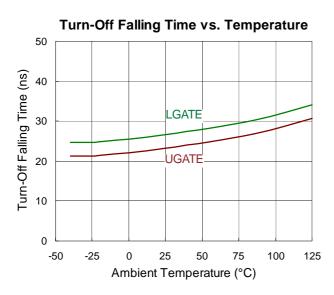

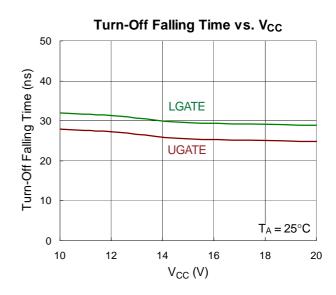

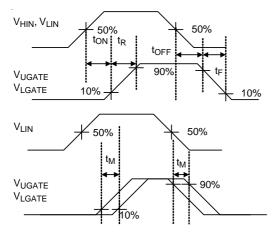

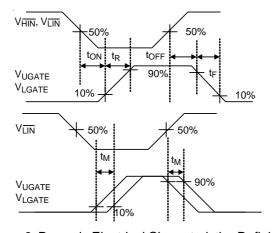

#### **Dynamic Electrical Characteristics (Note 4)**

(VCC = VBOOT - LX = 15V, LX = GND, CL = 1000pF, TA = 25°C, unless otherwise specified)

| Parameter                                  | Symbol         | Test Conditions                      | Min | Тур | Max | Unit |

|--------------------------------------------|----------------|--------------------------------------|-----|-----|-----|------|

| Turn-on Delay                              | ton            |                                      |     | 150 | 220 | ns   |

| Turn-off Delay                             | tOFF           | V <sub>LX</sub> = 0 or 600V (Note 5) |     | 150 | 220 | ns   |

| Turn-on Rising Time                        | t <sub>R</sub> |                                      |     | 70  | 170 | ns   |

| Turn-off Falling Time                      | t <sub>F</sub> |                                      |     | 35  | 90  | ns   |

| Delay Matching Time, HS and LS Turn-on/off | t <sub>M</sub> |                                      |     |     | 20  | ns   |

- Note 1. Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effectivethermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.

- **Note 3.** The device is not guaranteed to function outside its operating conditions.

- Note 4. Please refer to the Timing Diagram and Dynamic Waveforms in the Application Information.

- **Note 5.** Turn-off Delay for  $V_{LX} = 600V$  is guaranteed by design.

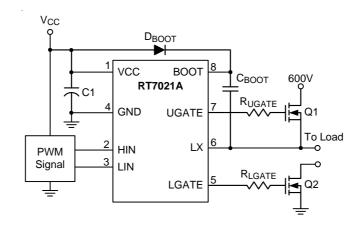

## **Typical Application Circuit**

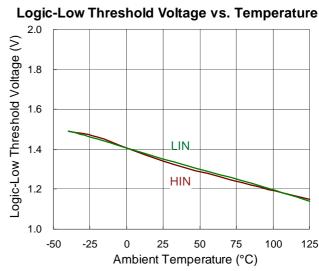

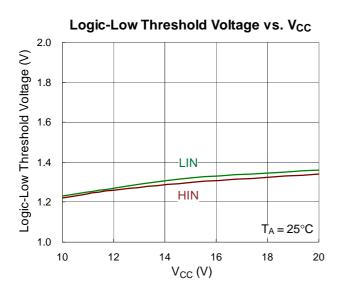

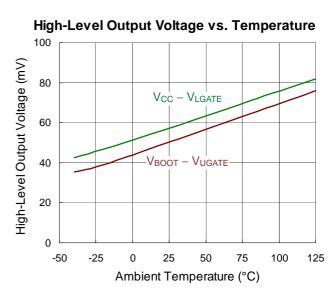

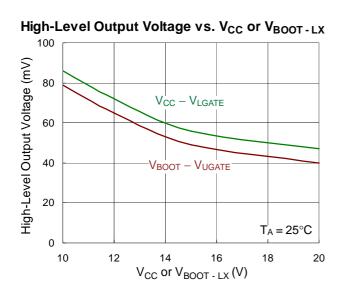

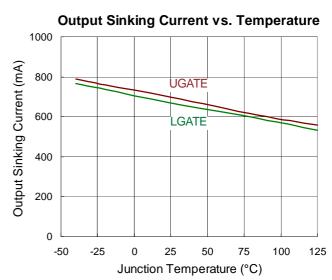

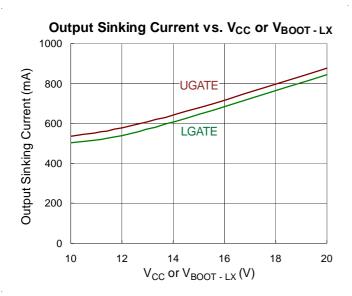

## **Typical Operating Characteristics**

### **Application Information**

#### **Timing Diagram and Dynamic Waveforms**

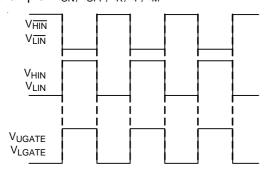

Figure 1 is RT7021A/B input / output timing diagram, and Figure 2, Figure 3 are the definition of dynamic characteristics. You can know those definitions and the relationship between input and output from these figures. For example:  $t_{ON}$ ,  $t_{OFF}$ ,  $t_R$ ,  $t_F$ ,  $t_M$ ...

Figure 1. Input/Output Timing Diagram

Figure 2. Dynamic Electrical Characteristics Definition for RT7021A

Figure 3. Dynamic Electrical Characteristics Definition for RT7021B

# Matched Propagation Delays between Both Channels

Because the IC internal level shifter circuit causes the propagation delay of the high-side output signal, shown in Figure 4. The RT7021A/B adds a propagation delay matching circuit in the low-side logic circuit, so that high-side and low-side output signals approximately synchronization.

Figure 4. Propagation Delay Matching Circuit

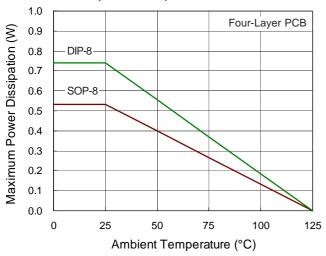

#### **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a SOP-8 package, the thermal resistance,  $\theta_{JA}$ , is 188°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity

four-layer test board. For a DIP-8 package, the thermal resistance, θ<sub>JA</sub>, is 134.9°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated as below:

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (188^{\circ}C/W) = 0.53W$  for a SOP-8 package.

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (134.9^{\circ}C/W) = 0.74W$  for a DIP-8 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed T<sub>J(MAX)</sub> and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 5 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 5. Derating Curve of Maximum Power Dissipation

#### **Layout Consideration**

A proper PCB layout for power supply can reduce unnecessary waveform noise and electromagnetic interference problems to ensure proper system operation, please refer to the following PCB layout considerations:

- > For the high voltage and high current loop layout of power supply should be as thick and short. Avoid excessive layout generated parasitic inductance and resistors to cause significant noise.

- ▶ In order to shorten the length of IC layout, you need to consider the relative placement for IC and the power switches. It is recommended that the power switches placed in a symmetrical manner, and the IC close to high-side and low-side elements.

- In order to reduce the noise coupling, it is recommended that the ground layout should not be placed under or near the high voltage floating side.

- The layout between high-side and low-side power switches should be thick and straight, avoiding the formation of long loops. Too long distance will increase the loop area, and electromagnetic interference suppression capabilities would be affected. However, too short distance may cause overheating situation. It is necessary to consider the most appropriate way.

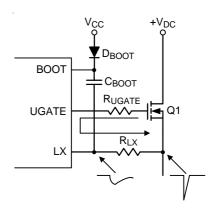

- Refer to typical application circuit, the VCC capacitor (C1), BOOT to LX capacitor (CBOOT), and bootstrap diode (D<sub>BOOT</sub>) need to be placed as close to the IC as possible to minimize parasitic inductance and resistance. The  $C_{BOOT}$  selected range is from  $0.1\mu F$  to  $0.47\mu F$ , and the VCC capacitor (C1) is greater than ten times C<sub>BOOT</sub>. It is recommended to use fast or ultra fast reverse recovery time bootstrap diode D<sub>BOOT</sub>.

- ▶ In Figure 6, the LX pin voltage drop can be improved by adding  $R_{LX}$  ( $R_{LX} = 1$  to  $10\Omega$ ), because the dv/dt is affected by  $(R_{LX} + R_{UGATE})$ .

Figure 6. LX Pin Resister

• If the gate current loop opens circuit for some factors, at this time the current flows through the gate loop via the power MOSFET drain-to-gate parasitic capacitor. The current will charge the gate-to-source parasitic capacitor to result in power MOSFET wrong action. The power switches can be damaged or burned out, the resisters (about least  $10k\Omega$ ) are connected between the gate and source pin can prevent malfunction of the power switches.

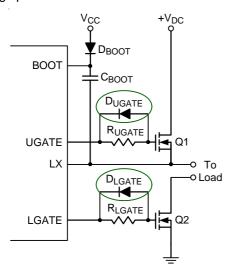

➤ The selection of larger parasitic capacitor power switch or gate resister may result in too long turn-off time making the high-side and low-side power switches shoot through. In order to prevent the situation, reverse parallel with diodes (D<sub>UGATE</sub> & D<sub>LGATE</sub>) in the R<sub>UGATE</sub> and R<sub>LGATE</sub> (shown in Figure 7), providing a fast discharge path for the power switches in a short time to complete the closing operation.

Figure 7. Reverse Parallel with Diodes

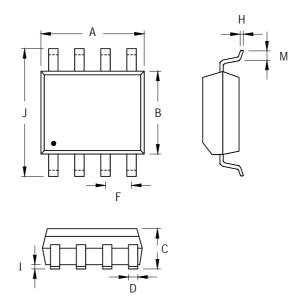

## **Outline Dimension**

| Symbol | Dimensions l | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

|        | Min          | Max           | Min                  | Max   |  |

| А      | 4.801        | 5.004         | 0.189                | 0.197 |  |

| В      | 3.810        | 3.988         | 0.150                | 0.157 |  |

| С      | 1.346        | 1.753         | 0.053                | 0.069 |  |

| D      | 0.330        | 0.508         | 0.013                | 0.020 |  |

| F      | 1.194        | 1.346         | 0.047                | 0.053 |  |

| Н      | 0.170        | 0.254         | 0.007                | 0.010 |  |

| l      | 0.050        | 0.254         | 0.002                | 0.010 |  |

| J      | 5.791        | 6.200         | 0.228                | 0.244 |  |

| М      | 0.400        | 1.270         | 0.016                | 0.050 |  |

8-Lead SOP Plastic Package

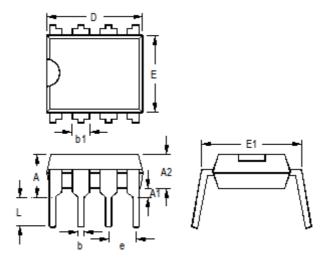

| Oh. a.l | Dimensions  | In Millimeters | Dimensions In Inches |       |  |

|---------|-------------|----------------|----------------------|-------|--|

| Symbol  | Min         | Max            | Min                  | Max   |  |

| А       | 3.700       | 4.320          | 0.146                | 0.170 |  |

| A1      | 0.381       | 0.710          | 0.015                | 0.028 |  |

| A2      | 3.200       | 3.600          | 0.126                | 0.142 |  |

| b       | 0.360       | 0.560          | 0.014                | 0.022 |  |

| b1      | 1.143       | 1.778          | 0.045                | 0.070 |  |

| D       | 9.050       | 9.550          | 0.356                | 0.376 |  |

| Е       | 6.200       | 6.600          | 0.244                | 0.260 |  |

| E1      | 7.620       | 8.255          | 0.300                | 0.325 |  |

| е       | 2.540       |                | 0.1                  | 00    |  |

| L       | 3.000 3.600 |                | 0.118                | 0.142 |  |

8-Lead DIP Plastic Package

#### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.