## **Laser Driver for Projectors**

### **General Description**

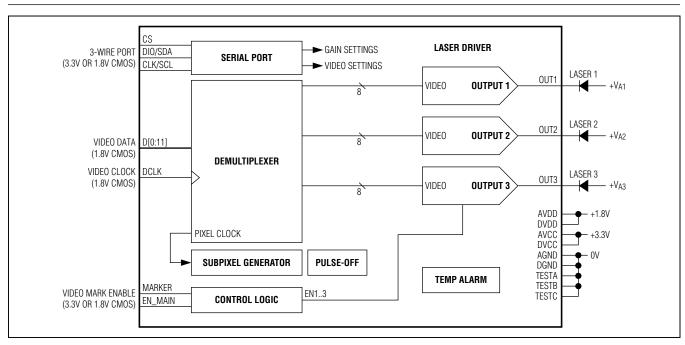

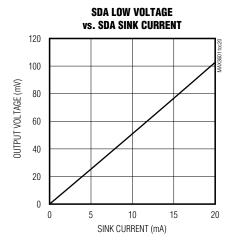

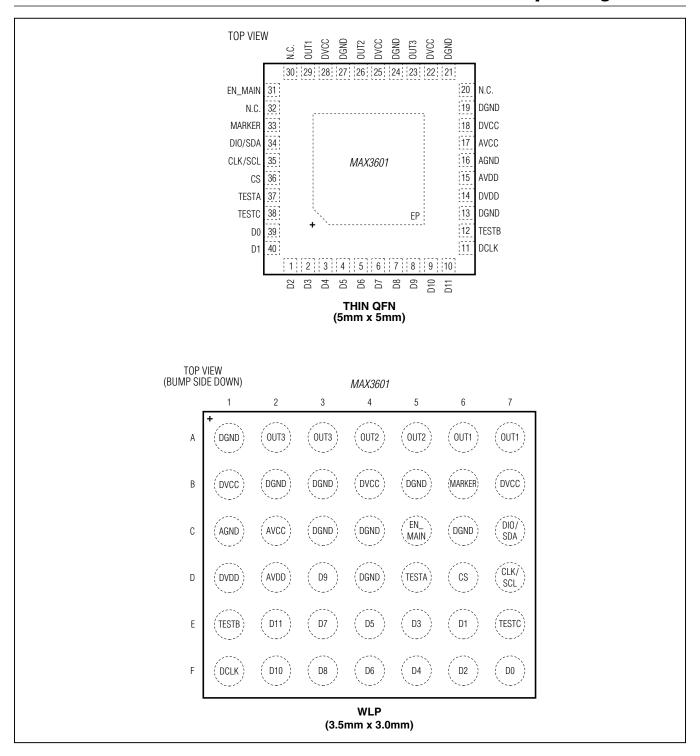

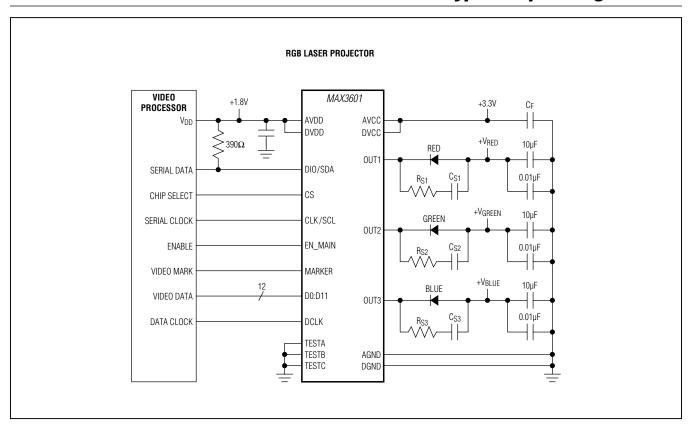

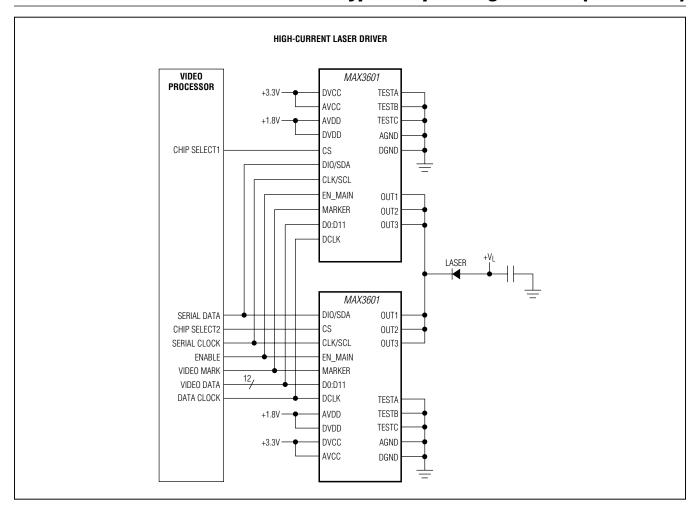

The MAX3601 laser driver for pico projectors supports video imaging with red, blue, and green lasers. Each output includes two 8-bit digital-to-analog converters (DACs) with programmable gain and up to 400mA driving capability per channel. DAC A has a full-scale current up to 320mA, while DAC B has full-scale current up to 80mA. All three channels can be combined into a single channel with up to 1.2A drive capability.

Maxim's patented technology allows pulsed current to operate lasers efficiently while reducing speckle. This feature operates from the video data clock. The driver is available in a 3.0mm x 3.5mm, 42-bump wafer-level package for commercial applications and a 5mm x 5mm, 40-pin TQFN package for industrial and automotive applications.

### **Applications**

RGB Pico Laser Projector

Laser Light Source for LCOS Projectors

High-Current LED or Laser Pulse Generator

Ordering Information appears at end of data sheet.

### **Benefits and Features**

- ♦ Integrates Three Current-Output Laser Drivers

- ♦ Compatible with Most Red, Blue, and Green Lasers

- ♦ 8-Bit Video DACs, DC to 167MHz operation

- ♦ Patented Pulsing Feature Reduces Laser Speckling

- ♦ 1ns Output Switching Time

- ♦ Pulse Switching Speed Enhancer

- ♦ Minimizes PCB Area with Functional Integration

- ♦ SPI or I<sup>2</sup>C Serial Port Control

- ♦ 1.8V to 3.3V Operation

- **♦ 8-Bit Gain Adjustment**

- ♦ Programmable Pulse Current

- ♦ Integrated Temperature Sensor

- **♦ Low Power Requirements**

- ♦ < 80mW for Black Video Images

</p>

- **♦ Output Disable Using Video Marker**

- ♦ Output Voltage Sensor

- **♦ Laser Enable Function Supports Safety Compliance**

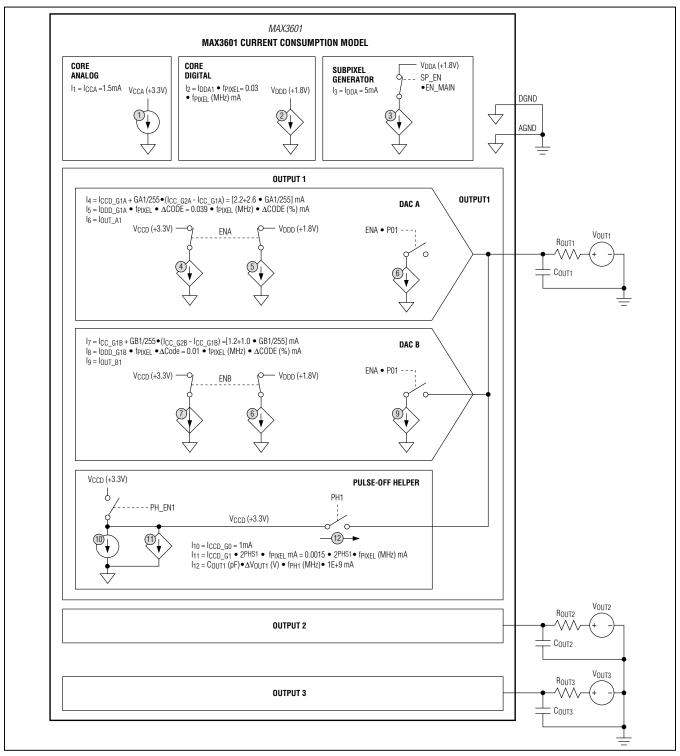

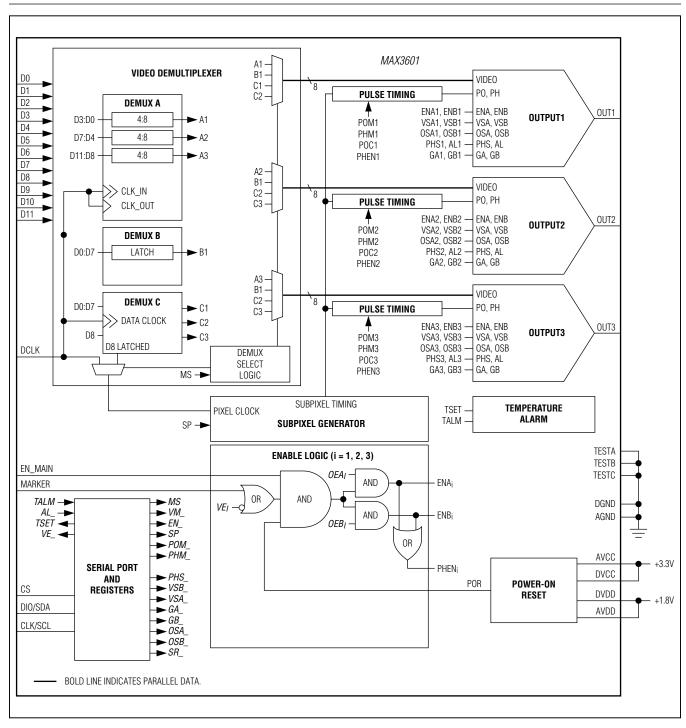

### **Simplified Functional Diagram**

For related parts and recommended products to use with this part, refer to: www.maximintegrated.com/MAX3601.related

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

# **Laser Driver for Projectors**

# TABLE OF CONTENTS

| General Description                      |    |

|------------------------------------------|----|

| Applications                             | 1  |

| Benefits and Features                    |    |

| Simplified Functional Diagram            |    |

| Absolute Maximum Ratings                 | 6  |

| Package Thermal Characteristics          | 6  |

| Electrical Characteristics               | 6  |

| Typical Operating Characteristics        |    |

| Pin/Bump Configurations                  |    |

| Pin/Bump Description                     | 19 |

| Functional Diagram                       | 21 |

| Detailed Description                     | 22 |

| Video Demultiplexer                      |    |

| Demux A                                  |    |

| Demux B                                  |    |

| Demux C                                  |    |

| Pulse Timing Generator                   | 24 |

| Subpixel Programming                     |    |

| Pulse-Off                                |    |

| Driver Outputs                           |    |

| Video DACs                               |    |

| Pulse-Off and Pulse-off Assist           |    |

| Compliance Voltage Sensor                |    |

| Temperature Alarm                        |    |

| Control Logic                            |    |

| Video Selection                          |    |

| Laser Control                            |    |

| Serial Port and Registers                |    |

| I <sup>2</sup> C Interface               | 30 |

| Data Transfer                            | 30 |

| START and STOP Conditions                | 30 |

| Acknowledge                              | 31 |

| Slave Address                            |    |

| I <sup>2</sup> C Communication Protocols |    |

| Writing to a Single Register             | 32 |

| Writing to Sequential Registers          |    |

# **Laser Driver for Projectors**

### **TABLE OF CONTENTS (continued)** Applications Information..... Wafer-Level Packaging (WLP) Applications Information......40 Ordering Information .....

# **Laser Driver for Projectors**

| LIST OF FIGURES                                        |    |

|--------------------------------------------------------|----|

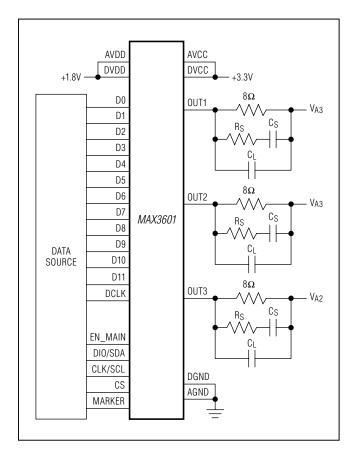

| Figure 1. Test Circuit                                 | 13 |

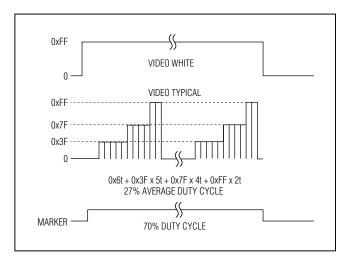

| Figure 2. Video Test Pattern                           | 13 |

| -igure 3. ΔCode Example                                | 13 |

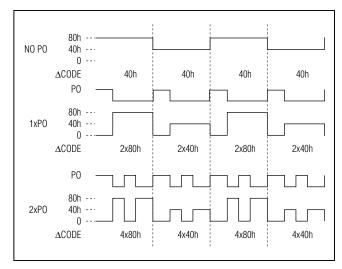

| Figure 4. Power-Supply Calculations                    | 14 |

| Figure 5. Video Demultiplexer A Input Waveform         | 22 |

| Figure 6. Video Demultiplexer B Input Waveform         | 22 |

| Figure 7. Video C Demultiplexer Input Waveform         | 23 |

| Figure 8. Video C Demultiplexer                        | 23 |

| Figure 9. Pulse Timing Generator                       | 24 |

| Figure 10. Driver Output                               | 26 |

| Figure 11. Driver Output Full-Scale Current Range      | 27 |

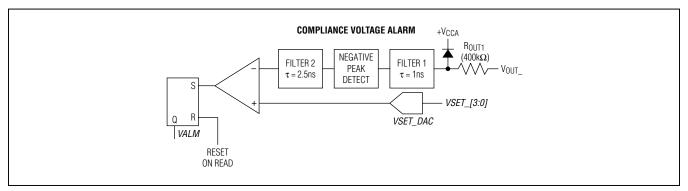

| Figure 12. Output Compliance Sensor                    | 28 |

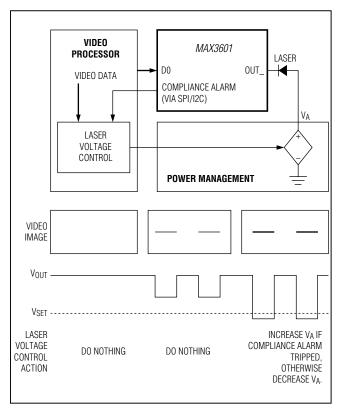

| Figure 13. Example Use of Compliance Sensor            | 28 |

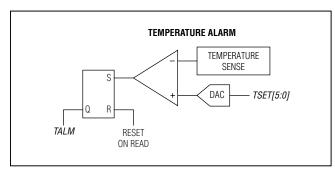

| Figure 14. Temperature Alarm                           | 29 |

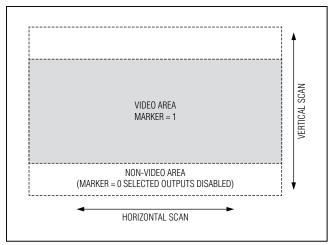

| Figure 15. Video Marker                                | 29 |

| Figure 16. I <sup>2</sup> C Master/Slave Configuration | 30 |

| Figure 17. I <sup>2</sup> C Bit Transfer               | 30 |

| Figure 18. I <sup>2</sup> C START and STOP Conditions  | 30 |

| Figure 19. I <sup>2</sup> C Acknowledge                | 31 |

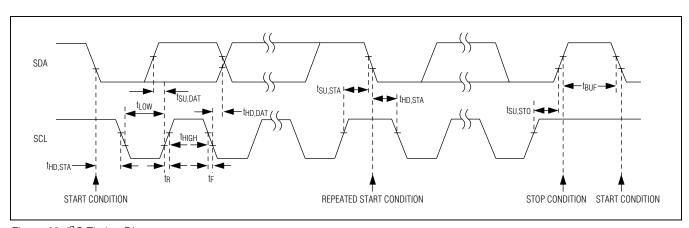

| Figure 20. I <sup>2</sup> C Timing Diagram             | 31 |

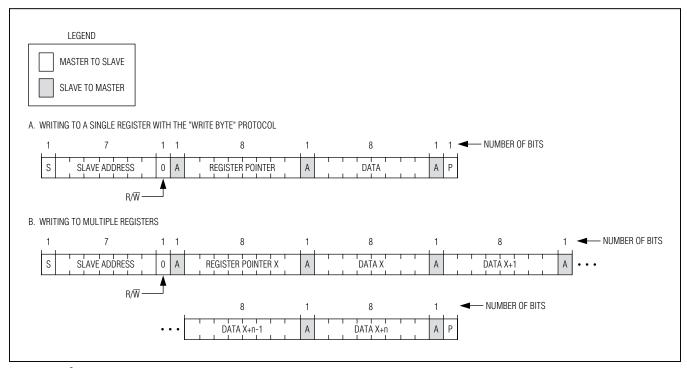

| Figure 21. I <sup>2</sup> C Writing                    | 32 |

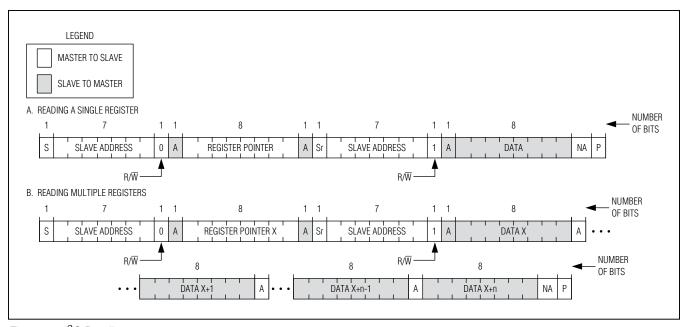

| Figure 22. I <sup>2</sup> C Reading                    | 33 |

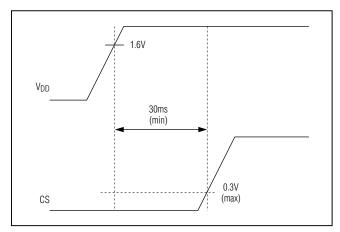

| Figure 23. AVDD, DVDD, and CS Timing for SPI Mode      | 34 |

| Figure 24. SPI Timing                                  | 34 |

| Figure 25. SPI Write Timing                            | 35 |

| Figure 26. SPI Read Timing                             | 35 |

| Figure 27. Power-Supply Sequencing                     | 39 |

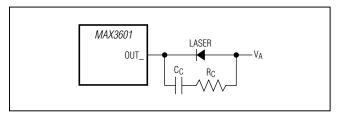

| Figure 28. Laser and Package Model                     | 39 |

| Figure 29. Optional Compensation Components            | 40 |

# **Laser Driver for Projectors**

| LIST OF TABLES                                           |    |

|----------------------------------------------------------|----|

| Table 1. Subpixel Programming (SP Register)              | 25 |

| Table 2. Pulse-Off Duty Cycle (POC_ Register)            | 25 |

| Table 3. Random Pulse-Off Programming                    | 25 |

| Table 4. Video Select Logic for DAC A                    | 27 |

| Table 5. Video Select Logic for DAC B                    | 27 |

| Table 6. Compliance Alarm Setpoint                       | 28 |

| Table 7. Video Demultiplexer Selection Logic             | 29 |

| Table 8. Register Table                                  | 36 |

| Table 9. Typical Laser Diode Parameters                  | 39 |

| Table 10. Detailed Register Table (see <u>Table 8</u> ). | 41 |

# **Laser Driver for Projectors**

#### **ABSOLUTE MAXIMUM RATINGS**

| DVDD to DGND         -0.3V to +2.2V         CS           AVCC to AGND         -0.3V to +4.0V         Cont           DVCC to DGND         -0.3V to +4.0V         TC           AVDD to DVDD         -0.3V to +0.3V         WI           AVCC to DVCC         -0.3V to +0.3V         Junc           AGND to DGND         -0.3V to +0.3V         Oper           OUT_ to DGND         -0.3V to +8.4V         TC           OUT_ Current         WI           Continuous         400mA         Stora           Peak (t < 1µs)         800mA         Leac | D-D11, DCLK, SCL, SDA, CS, EN_MAIN, MARKER Current50mA to +50mA ontinuous Power Dissipation TQFN (T <sub>A</sub> = +85°C, derate 35.7mW/°C above +85°C)2320mW WLP (T <sub>A</sub> = +70°C, derate 28.5mW/°C above +70°C)2200mW Inction Temperature+150°C Derating Temperature Range TQFN40°C to +105°C WLP0°C to +70°C Derating Temperature Range55°C to +150°C Derating Temperature (soldering, 10s; TQFN only)+300°C Idering Temperature (reflow)+260°C |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **PACKAGE THERMAL CHARACTERISTICS (Note 1)**

| TQFN                                                        | WLP                                                             |

|-------------------------------------------------------------|-----------------------------------------------------------------|

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )2°C/W | Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )36°C/W |

| Junction-to-Ambient Thermal Resistance (θ ιΔ)28°C/W         |                                                                 |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = V_{DVDD} = 1.7V \text{ to } 1.9V, V_{AVCC} = V_{DVCC} = 2.9V \text{ to } 3.5V, T_A = T_{MIN} \text{ to } T_{MAX}, T_J < +125^{\circ}C, EN\_MAIN \text{ and MARKER high, } V_{OUT} \geq 0.7V, \text{ unless otherwise noted. Typical values are at } V_{AVDD} = V_{DVDD} = 1.8V, V_{AVCC} = V_{DVCC} = 3.3V, T_J = +85^{\circ}C. \text{ Consumer grade parts are tested at } T_A = +70^{\circ}C. \text{ Automotive grade parts are tested at } T_A = +105^{\circ}C. \text{ Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)}(Note 2)$

| PARAMETER                    | SYMBOL                | CONDITIONS                                                                          | MIN | TYP  | MAX    | UNITS           |

|------------------------------|-----------------------|-------------------------------------------------------------------------------------|-----|------|--------|-----------------|

| OPERATING CONDITIONS         |                       |                                                                                     |     |      |        |                 |

| Output Voltage               | V <sub>OUT</sub>      | Output enabled                                                                      | 0.5 | 0.6  | 7.5    | V               |

| POWER SUPPLY (Note 3, Figure | e 4)                  |                                                                                     |     |      |        |                 |

|                              | I <sub>AVDD_DIS</sub> | EN_MAIN low or SP_EN = 1                                                            |     | 0.01 | (1)    | μΑ              |

|                              | I <sub>AVDD</sub>     | SP_EN High                                                                          |     | 5    | 7      | mA              |

|                              |                       | SP_EN = 0                                                                           |     | 0.02 | (0.03) |                 |

|                              | I <sub>DVDD1</sub>    | $SP_EN = 1$ , $f_{PO} = 75MHz$                                                      |     | 0.1  | (0.2)  | mA/MHz          |

| +1.8V Supply Current         | I <sub>DVDD_G1A</sub> | Video dependency DAC A                                                              |     | 1.1  | (1.5)  | μΑ/             |

|                              | I <sub>DVDD_G1B</sub> | Video dependency DAC B                                                              |     | 0.5  | (0.6)  | (MHz x<br>ΔCODE |

|                              | I <sub>DVDD</sub>     | Maximum digital supply current f <sub>PIXEL</sub> = 150MHz, f <sub>PO</sub> = 75MHz |     |      | (45)   | mA              |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = 1.7V \text{ to } 1.9V, V_{AVCC} = V_{DVCC} = 2.9V \text{ to } 3.5V, T_A = T_{MIN} \text{ to } T_{MAX}, T_J < +125^{\circ}C, EN\_MAIN \text{ and MARKER high, } V_{OUT} \geq 0.7V, \text{ unless otherwise noted. Typical values are at } V_{AVDD} = V_{DVDD} = 1.8V, V_{AVCC} = V_{DVCC} = 3.3V, T_J = +85^{\circ}C. \text{ Consumer grade parts are tested at } T_A = +70^{\circ}C. \text{ Automotive grade parts are tested at } T_A = +105^{\circ}C. \text{ Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)}(Note 2)$

| PARAMETER                         | SYMBOL                | CONDITIONS                                                               | CONDITIONS              |       |       | MAX    | UNITS  |

|-----------------------------------|-----------------------|--------------------------------------------------------------------------|-------------------------|-------|-------|--------|--------|

|                                   | l <sub>AVCC</sub>     | Core analog                                                              |                         |       | 1.5   | 1.8    |        |

|                                   | I <sub>DVCC_DIS</sub> | ENA_ = ENB_ = 0                                                          |                         | 0.01  | 0.1   |        |        |

|                                   | I <sub>DVCC_G1A</sub> | GA_ = 0x00 (per channel)                                                 |                         |       | 3.4   | 4.8    |        |

|                                   | I <sub>DVCC_G2A</sub> | GA_ = 0xFF (per channel)                                                 |                         |       | 8.2   | 9.1    |        |

| +3.3V Supply Current              | I <sub>DVCC_G1B</sub> | GB_ = 0x00 (per channel)                                                 |                         |       | 1.2   | 1.6    | mA     |

| Training Cappi, Cameri            |                       | OD 0FF (non-shares)                                                      | MAX3601C                |       | 2.5   | 2.8    |        |

|                                   | IDVCC_G2B             | GB_ = 0xFF (per channel)                                                 | MAX3601G                |       | 2.5   | 3.3    |        |

|                                   |                       | Maximum analog supply                                                    | MAX3601C                |       |       | (37.6) |        |

|                                   | lavcc                 | current GA_= GB_ = 0xFF,<br>ENA_ = ENB_ = 1                              | MAX3601G                |       |       | (39.1) |        |

|                                   | I <sub>CCD_G1</sub>   | PHS_= 0                                                                  |                         |       | 5     | (10)   |        |

| Pulse-Off Assist Current (Note 4) | I <sub>CCD_G2</sub>   | $f_{PO} = f_{POH} = 75MHz, f_{PIXEL} = C_L = 0pF, V_{OUT\_MIN} = 0.8V_T$ |                         |       | 2.3   | (4.6)  | µA/MHz |

|                                   |                       | Outputs off, clock stopped                                               |                         |       | 0.2   |        |        |

| Power In MAX3601 Driver (Note 5)  |                       | 0% video                                                                 |                         |       |       |        |        |

|                                   |                       | 27% video                                                                | 27% video               |       |       |        | mW     |

|                                   |                       | 100% video                                                               | 100% video              |       |       |        |        |

|                                   |                       | 27% video with pulse-off                                                 |                         | 150   |       |        |        |

|                                   |                       | 27% video with pulse-off ass                                             |                         | 160   |       |        |        |

|                                   |                       | I <sub>OUT</sub> /V <sub>AVDD</sub>                                      |                         | 1     |       |        |        |

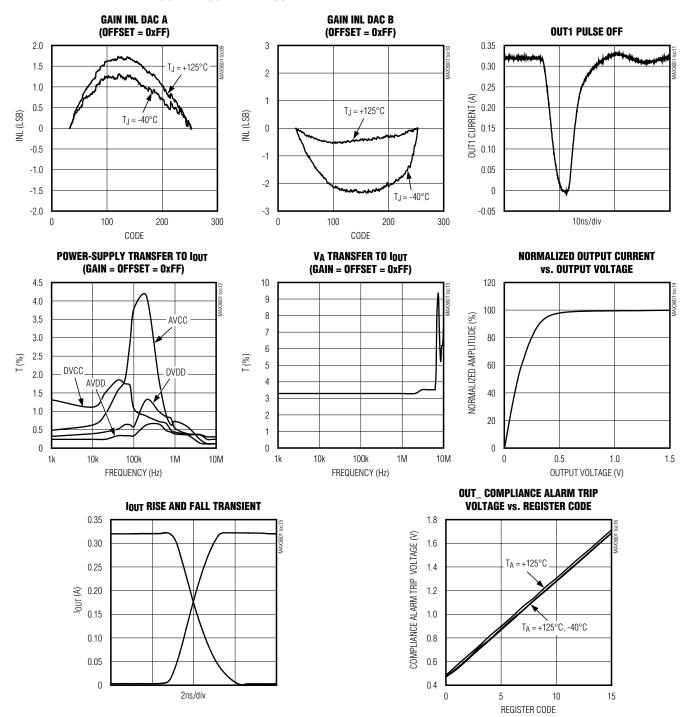

| Typical Output Sensitivity to     |                       | I <sub>OUT</sub> /V <sub>DVDD</sub>                                      |                         |       | 1     | (3)    | %/V    |

| Supply Voltage (Note 6)           |                       | I <sub>OUT</sub> /V <sub>AVCC</sub>                                      |                         |       | 2     | (17)   | 70/V   |

|                                   |                       | I <sub>OUT</sub> /V <sub>DVCC</sub>                                      |                         |       | 2.2   | (6)    |        |

| VIDEO DAC (8-Bit, Note 7)         |                       |                                                                          |                         |       |       |        |        |

| Maximum Conversion Rate           |                       |                                                                          |                         | 150   | 160   | (250)  | Msps   |

|                                   |                       | Within 12 LSBs (GAIN = 0x0F                                              | to 0xFF)                |       | 6.7   | (12)   |        |

| Settling Time                     | ts                    | Within 3 LSBs (GAIN = 0xFF)                                              | )                       |       | 12    | (25)   | ns     |

|                                   |                       | Within 1 LSB (GAIN = 0xFF)                                               |                         |       | 23    | (34)   |        |

| Rise/Fall Time                    |                       | 20% to 80%                                                               |                         | 1.5   | (2.5) | ns     |        |

| Offset Error (GSA_ = GSB+ =       | OS_ER                 | $0V \le V_{OUT} \le V_{AVCC} + 0.5V$                                     |                         |       | 1.0   | 24     | μA     |

| 0xFF, ENA_ = ENB_ = 1)            | OO_LI1                | V <sub>OUT</sub> = 7.5V                                                  |                         | (1.0) | 10.5  | 37     | μΛ     |

| Resistor ROUT1                    | R <sub>OUT1</sub>     | V <sub>OUT</sub> = 7.5V, see Figure 12                                   |                         | (290) | 400   | (490)  | kΩ     |

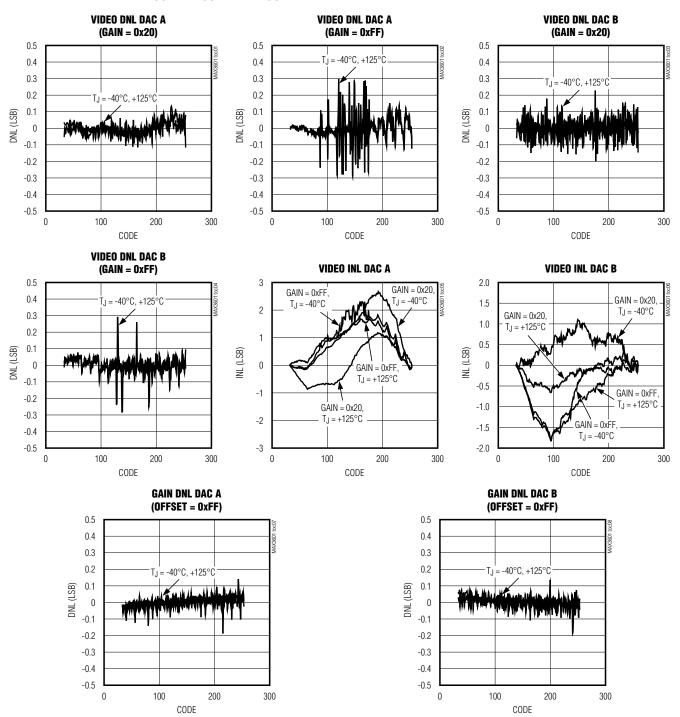

| Video INL (Notes 8 and 9)         |                       | Code > 0x1F                                                              |                         | (-15) |       | (15)   | LSB    |

| INL Drift (Notes 8 and 9)         |                       | 0x1F < GAIN < 0xFF, 0°C < 1<br>V <sub>OUT_MIN</sub> = 0.6V to 1.6V       | T <sub>J</sub> < +125°C |       | 1.5   | (3)    | LSB    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = 1.7V \text{ to } 1.9V, V_{AVCC} = V_{DVCC} = 2.9V \text{ to } 3.5V, T_A = T_{MIN} \text{ to } T_{MAX}, T_J < +125^{\circ}C, EN\_MAIN \text{ and MARKER high, } V_{OUT} \geq 0.7V, \text{ unless otherwise noted. Typical values are at } V_{AVDD} = V_{DVDD} = 1.8V, V_{AVCC} = V_{DVCC} = 3.3V, T_J = +85^{\circ}C. \text{ Consumer grade parts are tested at } T_A = +70^{\circ}C. \text{ Automotive grade parts are tested at } T_A = +105^{\circ}C. \text{ Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)}(Note 2)$

| PARAMETER                                                 | SYMBOL             | CONDITIONS                         |                                                   |       | TYP    | MAX    | UNITS           |  |

|-----------------------------------------------------------|--------------------|------------------------------------|---------------------------------------------------|-------|--------|--------|-----------------|--|

| Video DNL (GAIN = 0x0F to 0xFF) (Note 8)                  |                    | Guaranteed m                       | nonotonic                                         | (-1)  |        | (+1)   | LSB             |  |

| Propagation Delay (Delay = PD1                            |                    | PD1                                |                                                   |       | 2      |        | Pixel<br>clocks |  |

| + PD2)                                                    |                    | PD2                                |                                                   |       | 11     |        | ns              |  |

| Propagation Delay Variation                               |                    |                                    |                                                   | (-1)  |        | (+1)   | ns              |  |

|                                                           |                    | f < 50kHz, V <sub>O</sub>          | UT > 0.9V                                         |       | 0.2    | (1)    |                 |  |

| Transfer of V <sub>OUT</sub> to I <sub>OUT</sub> (Note 5) |                    | f < 1MHz, V <sub>Ol</sub>          | <sub>T</sub> > 0.6V                               |       | 6      | (10)   | %/V             |  |

|                                                           |                    | f < 1MHz, V <sub>Ol</sub>          | <sub>T</sub> > 0.5V                               |       | 12     | (15)   |                 |  |

| (0005                                                     |                    | $V_{OUT} = 0.6V$                   |                                                   |       | 260    |        |                 |  |

| Output Capacitance (CODE_A = CODE_B = 0x00)               | C <sub>DVR</sub>   | $V_{OUT} = 1.1V$                   |                                                   |       | 125    |        | рF              |  |

| CODE_B = 0x00)                                            |                    | $V_{OUT} = 2.0V$                   |                                                   |       | 100    |        |                 |  |

| PULSE OFF ASSIST                                          |                    |                                    |                                                   |       |        |        |                 |  |

| Rise Time                                                 |                    | 20% to 80%, \PHS_ = 3, VID         | $V_{A_{-}} = 1.0V, C_{L} = 0pF,$<br>0EO = 0x00    |       | 1.6    | (3)    | ns              |  |

|                                                           |                    | PHS_= 3,                           |                                                   |       | 8      |        |                 |  |

| Incremental Resistance                                    |                    | PHS_= 2                            |                                                   |       | 16     |        |                 |  |

| PH_= 0xFFFF                                               |                    | PHS_= 1                            |                                                   | 32    |        | Ω      |                 |  |

|                                                           |                    | PHS_= 0                            |                                                   |       | 64     |        |                 |  |

| Compliance Voltage                                        | V <sub>O_POH</sub> | Relative to V <sub>A</sub> +125°C) | $VCC$ , $I_{OUT} = 1mA$ ( $T_A = 0$ to            |       |        | (-0.8) | V               |  |

|                                                           | 0_1 011            | $T_A = -40$ °C to                  |                                                   |       | (-0.9) |        |                 |  |

| OUTPUT GAIN (VIDEO_ = 0xFF)                               |                    |                                    |                                                   | ,     |        |        |                 |  |

| Resolution                                                |                    |                                    |                                                   |       | 8      |        | Bits            |  |

|                                                           |                    | GA_= 0x00, G                       | 6B_= 0x00                                         |       | 0.01   | (1)    |                 |  |

|                                                           |                    |                                    | MAX3601C                                          | 280   | 320    | 400    |                 |  |

|                                                           |                    | GA_= 0xFF,<br>GB_= 0x00            | MAX3601G, $T_A = +25^{\circ}C$ to $+105^{\circ}C$ | 275   | 320    | 400    |                 |  |

|                                                           |                    |                                    | MAX3601G, T <sub>A</sub> < +25°C                  | 260   | 320    | 400    |                 |  |

| Current at OUT                                            |                    |                                    | MAX3601C                                          | 69    | 80     | 100    | mA              |  |

|                                                           |                    | GA_= 0x00,<br>GB_= 0xFF            | MAX3601G, $T_A = +25^{\circ}C$ to $+105^{\circ}C$ | 68    | 80     | 100    |                 |  |

|                                                           |                    |                                    | MAX3601G, T <sub>A</sub> < +25°C                  | 60    | 80     | 100    |                 |  |

|                                                           |                    | GA_= 0xFF,                         | MAX3601C                                          | (349) | 400    | (500)  |                 |  |

|                                                           |                    | GB_= 0xFF                          | MAX3601G                                          | (320) | 400    | (500)  |                 |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = 1.7V \text{ to } 1.9V, V_{AVCC} = V_{DVCC} = 2.9V \text{ to } 3.5V, T_A = T_{MIN} \text{ to } T_{MAX}, T_J < +125^{\circ}C, EN\_MAIN \text{ and } MARKER \text{ high, } V_{OUT} \ge 0.7V, \text{ unless otherwise noted. Typical values are at } V_{AVDD} = V_{DVDD} = 1.8V, V_{AVCC} = V_{DVCC} = 3.3V, T_J = +85^{\circ}C. \text{ Consumer grade parts are tested at } T_A = +70^{\circ}C. \text{ Automotive grade parts are tested at } T_A = +105^{\circ}C. \text{ Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)}(Note 2)$

| PARAMETER                     | SYMBOL                | CONDIT                                               | MIN                         | TYP    | MAX   | UNITS                      |        |

|-------------------------------|-----------------------|------------------------------------------------------|-----------------------------|--------|-------|----------------------------|--------|

| COMPLIANCE ALARM              | •                     |                                                      |                             |        |       |                            |        |

| VSET DAC Resolution           |                       | 4 bit                                                |                             | (70)   | 80    | (90)                       | mV     |

| VOET DAG D                    |                       | VSET_ = 0x0                                          | VSET_ = 0x0                 |        |       |                            | .,     |

| VSET DAC Range                |                       | VSET_ = 0xF                                          |                             | 1.4    | 1.6   | 1.8                        | V      |

| Filter 1 Time Constant        |                       |                                                      |                             |        | 1     |                            | ns     |

| Filter 2 Time Constant        |                       |                                                      |                             |        | 2.7   |                            | ns     |

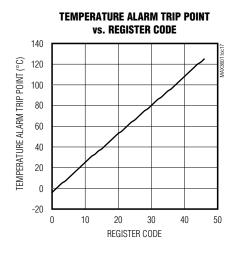

| TEMPERATURE ALARM             | •                     |                                                      |                             |        |       |                            |        |

| Temperature Range             |                       |                                                      |                             | (5)    |       | (150)                      | °C     |

| Temperature Accuracy          |                       | $T_J = +20^{\circ}\text{C to } +125^{\circ}\text{C}$ |                             | (-10)  |       | (10)                       | °C     |

| Temperature Resolution        |                       | $T_J = +20^{\circ}\text{C to } +125^{\circ}\text{C}$ |                             | (2.25) | 2.5   | (2.75)                     | °C/LSB |

| LOGIC I/O (DIO/SDA, CLK/SCL,  | CS, MARKER            | R, EN_MAIN)                                          |                             | ·      |       |                            |        |

| Input Low Voltage             | V <sub>IL2</sub>      | Test condition                                       |                             |        |       | 0.4                        | V      |

| Input High Voltage            | V <sub>IH2</sub>      | Test condition                                       |                             | 1.45   |       |                            | V      |

| Input High Threshold          |                       | Relative to V <sub>DVDD</sub>                        | (50)                        | 60     | (70)  | %                          |        |

| Input Low Threshold           |                       | Relative to V <sub>DVDD</sub>                        | (40                         | 50     | (60)  | %                          |        |

| Input Hysteresis              |                       | Relative to V <sub>DVDD</sub>                        | (5)                         |        |       | %                          |        |

| Input Current                 |                       | DIO/SDA, CLK/SCL                                     | -10                         | ±0.2   | +10   | μΑ                         |        |

|                               | R <sub>EN_MAIN</sub>  | EN_MAIN to DGND                                      | 50                          | 100    | 200   |                            |        |

| Input Resistance              | R <sub>MARKER</sub>   | MARKER to DVDD                                       | 50                          | 100    | 200   | kΩ                         |        |

|                               | R <sub>CS</sub>       | CS to DGND                                           |                             | 50     | 100   | 200                        |        |

| Input Capacitance             |                       |                                                      |                             |        | 1     |                            | рF     |

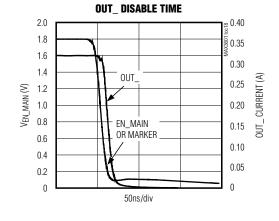

| Disable Time                  | t <sub>DIS</sub>      | EN_MAIN or MARKER                                    | to I <sub>OUT</sub> falling |        | 0.1   | 1                          | μs     |

| Enable Settling Time Constant | t <sub>EN</sub>       | EN_MAIN rising or MAF                                | RKER rising                 |        | 0.5   | 1.5                        | μs     |

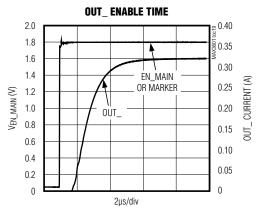

| DIO/SDA Low Voltage           |                       | I <sub>DIO/SDA</sub> = 16mA                          |                             |        | 0.1   | 0.4                        | V      |

| VIDEO DATA INPUTS             |                       |                                                      |                             |        |       |                            |        |

| Maximum Frequency             | f <sub>DCLK_MAX</sub> |                                                      |                             | 150    | > 160 |                            | MHz    |

| DCLK Duty Cycle               |                       | f <sub>DCLK</sub> > 100MHz                           |                             | (45)   |       | (55)                       | %      |

| DCLK High Time                |                       | Relative to 2/f <sub>DCLK</sub>                      |                             | (-0.5) |       | (+0.5)                     | ns     |

| Video Input Setup Time        | t <sub>SU</sub>       | Operating condition                                  |                             | 1      |       |                            | ns     |

|                               |                       |                                                      | MAX3601C                    | 0.25   |       |                            |        |

| Video Input Hold Time         | t <sub>H</sub>        | Operating condition                                  | MAX3601G                    | 0.35   |       |                            | ns     |

| Input Switching Time          |                       | 10% to 90%, operating                                | condition                   |        | 1.2   |                            | ns     |

|                               |                       |                                                      |                             |        |       | 0.5 x                      |        |

| Input Low Voltage             | V <sub>IN-L</sub>     |                                                      |                             |        |       | V <sub>DVDD</sub><br>- 0.1 | V      |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = 1.7V \text{ to } 1.9V, V_{AVCC} = V_{DVCC} = 2.9V \text{ to } 3.5V, T_A = T_{MIN} \text{ to } T_{MAX}, T_J < +125^{\circ}C, EN\_MAIN \text{ and MARKER high, } V_{OUT} \geq 0.7V, \text{ unless otherwise noted. Typical values are at } V_{AVDD} = V_{DVDD} = 1.8V, V_{AVCC} = V_{DVCC} = 3.3V, T_J = +85^{\circ}C. \text{ Consumer grade parts are tested at } T_A = +70^{\circ}C. \text{ Automotive grade parts are tested at } T_A = +105^{\circ}C. \text{ Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)}(Note 2)$

| PARAMETER                            | SYMBOL              | CONDITIONS                           | MIN                                 | TYP  | MAX    | UNITS |

|--------------------------------------|---------------------|--------------------------------------|-------------------------------------|------|--------|-------|

| Input High Voltage                   | V <sub>IN-H</sub>   |                                      | 0.5 x<br>V <sub>DVDD</sub><br>+ 0.1 |      |        | V     |

| Input Threshold                      |                     | Relative to V <sub>DVDD</sub>        |                                     | 50   |        | %     |

| Input Hysteresis                     |                     |                                      |                                     | 0.1  |        | V     |

| Input Current                        |                     |                                      | -10                                 | <±1  | +10    | μΑ    |

| Data Input Capacitance               | C <sub>D</sub>      |                                      |                                     | 1    |        | рF    |

| SUBPIXEL GENERATOR                   |                     |                                      |                                     |      |        |       |

| Pixel Clock Frequency Range          |                     | Subpixel generator active            | 24                                  | 150  | (250)  | MHz   |

| Minimum Pulse Width                  |                     | 1 subpixel                           |                                     |      | (2)    | ns    |

| Subpixel Timing Accuracy             |                     | T <sub>PODM</sub> - T <sub>POD</sub> | (-1)                                |      | (+1)   | ns    |

| PLL Bandwidth                        |                     |                                      | (1200)                              | 2000 | (3100) | kHz   |

| I <sup>2</sup> C TIMING              |                     |                                      |                                     |      |        |       |

| Clock Frequency                      | f <sub>SCL</sub>    |                                      |                                     |      | 400    | kHz   |

| Bus Free Time Between START and STOP | t <sub>BUF</sub>    |                                      | 1.3                                 |      |        | μs    |

| HOLD Time for a START Condition      | t <sub>HD_STA</sub> |                                      | 0.6                                 |      |        | μs    |

| Setup Time Repeated START Condition  | tsu_sta             |                                      | 0.6                                 |      |        | μs    |

| SCL Low Time                         | t <sub>LOW</sub>    |                                      | 1.3                                 |      |        | μs    |

| SCL High Time                        | tHIGH               |                                      | 0.6                                 |      |        | μs    |

| SDA Hold Time                        | t <sub>HD_DAT</sub> |                                      | 0.1                                 |      | 0.6    | μs    |

| SDA Setup Time                       | t <sub>SU_DAT</sub> |                                      | 0.1                                 |      |        | μs    |

| Setup Time for STOP Condition        | t <sub>SU_STO</sub> |                                      | 0.6                                 |      |        | μs    |

| Pulse Width of Suppressed Spikes     | t <sub>SP</sub>     |                                      |                                     | 0.05 |        | μs    |

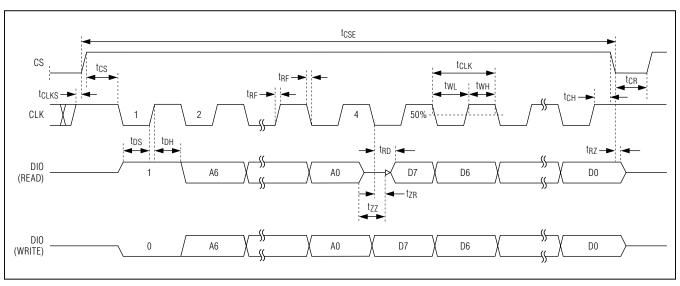

| SPI TIMING                           | '                   |                                      | ,                                   |      |        |       |

| SPI Clock Cycle                      | tCLK                |                                      | 83                                  |      |        | ns    |

| SCL High Pulse Width                 | t <sub>WH</sub>     |                                      | 41.5                                |      |        | ns    |

| SCL Low Pulse Width                  | t <sub>WL</sub>     |                                      | 41.5                                |      |        | ns    |

| SCL Rise/Fall Time                   | t <sub>RF</sub>     | At f <sub>CLK</sub> = 12MHz          |                                     | 16   |        | ns    |

| SCL Setup Time                       | tCLKS               |                                      | 8                                   |      |        | ns    |

| CS Setup/Hold Time                   | t <sub>CS</sub> ,   |                                      | 32                                  |      |        | ns    |

| CS Recovery Time                     | t <sub>CR</sub>     |                                      | 50                                  |      |        | ns    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = 1.7V \text{ to } 1.9V, V_{AVCC} = V_{DVCC} = 2.9V \text{ to } 3.5V, T_A = T_{MIN} \text{ to } T_{MAX}, T_J < +125^{\circ}C, EN\_MAIN \text{ and MARKER high, } V_{OUT} \ge 0.7V, \text{ unless otherwise noted. Typical values are at } V_{AVDD} = V_{DVDD} = 1.8V, V_{AVCC} = V_{DVCC} = 3.3V, T_J = +85^{\circ}C. \text{ Consumer grade parts are tested at } T_A = +70^{\circ}C. \text{ Automotive grade parts are tested at } T_A = +105^{\circ}C. \text{ Minimum and maximum specifications are guaranteed by design, characterization and/or production test.)}(Note 2)$

| PARAMETER                                          | SYMBOL             | CONDITIONS                               | MIN   | TYP  | MAX   | UNITS |

|----------------------------------------------------|--------------------|------------------------------------------|-------|------|-------|-------|

| Write Data Setup Time                              | t <sub>DS</sub>    |                                          | 16    |      |       | ns    |

| Write Data Hold Time                               | t <sub>DH</sub>    |                                          | 16    |      |       | ns    |

| Read Data Delay Time                               | t <sub>RD</sub>    |                                          |       |      | 34    | ns    |

| DIO Output Switching Time                          | t <sub>ZR</sub>    | $R_{DIO} = 390\Omega$ , $C_{DIO} = 20pF$ |       | 11   | (16)  | ns    |

| DIO Output Disable Time                            |                    | MAX3601C                                 |       |      | 34    |       |

|                                                    | t <sub>RZ</sub>    | MAX3601G                                 |       |      | 36    | ns    |

| DIO Conflict Avoid Time                            | t <sub>ZZ</sub>    |                                          | 0     |      |       | ns    |

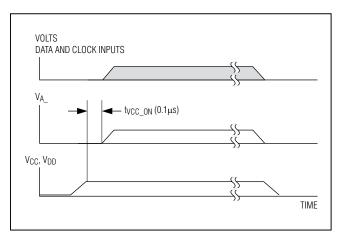

| POWER-ON RESET (Figure 27)                         |                    |                                          |       |      |       |       |

| V <sub>AVDD</sub> ,V <sub>DVDD</sub> On Threshold  | 2V <sub>POR+</sub> |                                          |       | 1.32 | (1.6) | V     |

| V <sub>AVDD</sub> ,V <sub>DVDD</sub> Off Threshold | 2V <sub>POR-</sub> |                                          | (1)   | 1.28 |       | V     |

| V <sub>DVCC</sub> ,V <sub>DVCC</sub> On Threshold  | 3V <sub>POR+</sub> |                                          |       | 2.5  | (2.8) | V     |

| V <sub>AVCC</sub> ,V <sub>DVCC</sub> Off Threshold | 3V <sub>POR-</sub> |                                          | (2.2) | 2.4  |       | V     |

Note 2: Parameters measured using circuit of <u>Figure 1</u>. R<sub>S</sub>, C<sub>S</sub>, C<sub>L</sub> = open, unless otherwise noted. Parameters in parentheses ( ) are provided for guidance, but are not tested or guaranteed.

Note 3: Power Consumption Calculations:

$$\begin{split} I_{DVDD}(mA) &= I_{DVDD}(mA/MHz) \times f_{PIXEL}(MHz) + \\ &\sum_{N=1}^{3} \left[ \text{ENA}_{N} \times I_{DVDD_{G1A}}(mA/MHz) \times \Delta \text{CODE}_{A_{N}} + \text{ENB}_{N} \times I_{DVDD_{G1B}}(mA/MHz) \times \Delta \text{CODE}_{B_{N}} \right] + f_{PIXEL}(MHz) \end{split}$$

$$I_{DVCC}(mA) = \sum_{N=1}^{3} \left[ ENA_{N} \times I_{DVCCD_{G1A}} + \left( I_{DVCC_{G2A}} - I_{DVCC_{G1A}} \right) \times \frac{GA_{N}}{255} + ENB_{N} \times I_{DVCC_{G1B}} + \left( I_{DVCC_{G2B}} - I_{DVCC_{G1B}} \right) \times \frac{GB_{N}}{255} \right]$$

where:

N = OUTPUT 1,2,3,  $f_{PIXEL}$  is the pixel clock frequency (MHz), ENA\_ and ENB\_ are the DAC enable signals with value 0 or 1,  $\Delta$ CODE is the average number of video code changes per pixel (0 to 255). If the Pulse-Off feature is used 1 time per pixel,  $\Delta$ CODE = 2x Average Video Code Value. If Pulse-Off is used 2 times per pixel,  $\Delta$ CODE = 4x Average Video Code Value (Figure 3).

Note 4: Pulse-Off Assist Current Calculation:

$$I_{DVCCD} \approx \sum_{N=1}^{3} \left[ \left( I_{DVCC_{G1}} + C_{OUTN} \times \Delta V_{OUTN} \right) \times f_{PON} \right]$$

where

N = Output 1,2,3,  $C_{OUTN}$  is the total capacitance at OUTN (MAX3601 output capacitance + external capacitance),  $\Delta V_{OUTN}$  is the resulting voltage change at OUTN,  $f_{PON}$  is the frequency of pulse-events in MHz.  $f_{PON}$  is generally equal to the pixel clock, but could be lower or higher, depending on the pulse-off duty cycle and number of pulse-off events per pixel.

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = 1.7V \text{ to } 1.9V, V_{AVCC} = V_{DVCC} = 2.9V \text{ to } 3.5V, T_A = T_{MIN} \text{ to } T_{MAX}, T_J < +125^{\circ}C, EN\_MAIN \text{ and MARKER high,} V_{OUT} \ge 0.7V, unless otherwise noted. Typical values are at <math>V_{AVDD} = V_{DVDD} = 1.8V, V_{AVCC} = V_{DVCC} = 3.3V, T_J = +85^{\circ}C$ . Consumer grade parts are tested at  $T_A = +70^{\circ}C$ . Automotive grade parts are tested at  $T_A = +105^{\circ}C$ . Minimum and maximum specifications are quaranteed by design, characterization and/or production test.)(Note 2)

Note 5: Power Estimation Conditions:

For each output, DAC A is enabled, DAC B is off, VIDEO = 27% data as shown in Figure 2,  $f_{PIXEL}$  = 150MHz. Vertical Image Duty cycle is 70%, and the MARKER signal is used to reduce power during vertical flyback.

The load emulates: Red Laser on OUT1: 4I + 2.3V

Green Laser on OUT2: 8I + 3.8V Blue Laser on OUT3: 16I + 3.5V

|   | PARAMETER                | VIDEO | GAIN1<br>(mA) | GAIN2<br>(mA) | GAIN3<br>(mA) | V <sub>OUT</sub><br>@I <sub>PEAK</sub> | VA1<br>(V) | VA2<br>(V) | VA3<br>(V) | PO_EN | POC | POM_  | PHM_  |

|---|--------------------------|-------|---------------|---------------|---------------|----------------------------------------|------------|------------|------------|-------|-----|-------|-------|

| 1 | 0% Video                 | 00h   | 200           | 180           | 70            | 0.6V                                   | 3.7        | 5.9        | 5.2        | 0     | 0   | 0     | 0     |

| 2 | 27% Video                | 27%   | 200           | 180           | 70            | 0.6V                                   | 3.7        | 5.9        | 5.2        | 0     | 0   | 0     | 0     |

| 3 | 100% Video               | FFh   | 200           | 180           | 70            | 0.6V                                   | 3.7        | 5.9        | 5.2        | 0     | 0   | 0     | 0     |

| 4 | Pulse-Off                | 27%   | 300           | 270           | 105           | 0.8V                                   | 4.3        | 6.8        | 6.0        | 1     | 4h  | FF00h | 0     |

| 5 | With Pulse-off<br>Assist | 27%   | 300           | 270           | 105           | 0.8V                                   | 4.3        | 6.8        | 6.0        | 1     | 4h  | FF00h | FF00h |

Note 6: Transfer from supply to I<sub>OUT</sub> measured with 100mV<sub>P-P</sub> sine wave applied at the supply.

$$T = \frac{f'I_{OUT}}{I_{OUT}} \times \frac{100\%}{f'V}$$

with units %/V.  $I_{OUT}$  = 325mA,  $T_{J} \le +110^{\circ}$ C,  $f_{OUT}$  = 60Hz to 1MHz. Typical values are at 10kHz, maximum value at 1MHz typical corner.

Note 7: AC Parameters characterized with a video pattern of 0x00 to 0xFF, GAIN = 0xFF, 0x3F, 0x1F, 0x0F. All combinations of output VIDEO DACs: DAC A only, DAC B only, DAC A and DAC B. An external filter network (R<sub>S</sub>, C<sub>S</sub>) or digital filter may be used to reduce ringing.

**Note 8:**

$$1 lsb = \frac{l_{OUT(CODE=0xFF)} - l_{OUT(CODE=0x00)}}{255}$$

Note 9: Integral nonlinearity (INL) is measured as: [IOUT - Least Squares approximation of current].

# **Laser Driver for Projectors**

Figure 1. Test Circuit

Figure 2. Video Test Pattern

Figure 3. ACode Example

# **Laser Driver for Projectors**

Figure 4. Power-Supply Calculations

# **Laser Driver for Projectors**

### **Typical Operating Characteristics**

$(V_{AVDD} = V_{DVDD} = 1.8V, V_{AVCC} = V_{DVCC} = 3.3V, V_{OUT} = 0.7V, R_L = 8\Omega, EN\_MAIN \ high, T_A = +25^{\circ}C, unless \ otherwise \ noted.)$

# **Laser Driver for Projectors**

### **Typical Operating Characteristics (continued)**

$(V_{AVDD} = V_{DVDD} = 1.8V, V_{AVCC} = V_{DVCC} = 3.3V, V_{OUT} = 0.7V, R_L = 8\Omega, EN\_MAIN \ high, T_A = +25^{\circ}C, unless \ otherwise \ noted.)$

# **Laser Driver for Projectors**

### **Typical Operating Characteristics (continued)**

$(V_{AVDD} = V_{DVDD} = 1.8V, V_{AVCC} = V_{DVCC} = 3.3V, V_{OUT} = 0.7V, R_L = 8\Omega, EN\_MAIN \ high, T_A = +25^{\circ}C, unless \ otherwise \ noted.)$

# **Laser Driver for Projectors**

### **Pin/Bump Configurations**

# **Laser Driver for Projectors**

## **Pin/Bump Description**

| Р                     | IN                                      |                           |                                                                                                                                                                                       |                            |  |  |  |

|-----------------------|-----------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|

| TQFN-EP               | WLP                                     | NAME                      | FUNCTION                                                                                                                                                                              | EQUIVALENT INPUT SCHEMATIC |  |  |  |

| 1                     | F6                                      | D2                        |                                                                                                                                                                                       |                            |  |  |  |

| 2                     | E5                                      | D3                        |                                                                                                                                                                                       |                            |  |  |  |

| 3                     | F5                                      | D4                        | 1                                                                                                                                                                                     |                            |  |  |  |

| 4                     | E4                                      | D5                        | Synchronous Video Data Inputs                                                                                                                                                         | DVDD                       |  |  |  |

| 5                     | F4                                      | D6                        |                                                                                                                                                                                       | DIGITAL                    |  |  |  |

| 6                     | E3                                      | D7                        |                                                                                                                                                                                       | INPUT T                    |  |  |  |

| 7                     | F3                                      | D8                        | Synchronous Video Data Input. In DEMUX C mode, D8 functions as the pixel clock.                                                                                                       | DGND                       |  |  |  |

| 8                     | D3                                      | D9                        |                                                                                                                                                                                       | - DGND                     |  |  |  |

| 9                     | F2                                      | D10                       | Synchronous Video Data Inputs                                                                                                                                                         |                            |  |  |  |

| 10                    | E2                                      | D11                       | Synchronous Video Data Input, MSB                                                                                                                                                     |                            |  |  |  |

| 11                    | F1                                      | DCLK                      | Video Clock Input                                                                                                                                                                     |                            |  |  |  |

| 12, 37, 38            | D5, E1, E7                              | TESTA,<br>TESTB,<br>TESTC | Test Pins. Connect to DGND.                                                                                                                                                           | _                          |  |  |  |

| 13, 19, 21,<br>24, 27 | A1, B2,<br>B3, B5,<br>C3, C4,<br>C6, D4 | DGND                      | Digital Ground. Connect to 0V.                                                                                                                                                        | _                          |  |  |  |

| 14                    | D1                                      | DVDD                      | 1.8V Digital Power Supply. Bypass DVDD to DGND with 0.1µF and 0.01µF capacitors as close as possible to the device with the smaller value capacitor closest to DVDD.                  |                            |  |  |  |

| 15                    | D2                                      | AVDD                      | 1.8V Analog Power Supply. Bypass AVDD to AGND with 0.1µF and 0.01µF capacitors as close as possible to the device with the smaller capacitor closest to AVDD.                         | _                          |  |  |  |

| 16                    | C1                                      | AGND                      | Analog Ground. Connect to 0V.                                                                                                                                                         | _                          |  |  |  |

| 17                    | C2                                      | AVCC                      | 3.3V Analog Power Supply. Bypass AVCC to AGND with 0.1µF and 0.01µF capacitors as close as possible to the device with the smaller capacitor closest to AVCC.                         | _                          |  |  |  |

| 18, 22, 25,<br>28     | B1, B4, B7                              | DVCC                      | 3.3V Digital Power Supply. Bypass DVCC to DGND with 0.1µF and 0.01µF capacitors (1 pair per pin) as close as possible to the device with the smaller value capacitor closest to DVCC. | _                          |  |  |  |

| 20, 30, 32            | _                                       | N.C.                      | No Connection. There is no connection from the package to the IC.                                                                                                                     | _                          |  |  |  |

# **Laser Driver for Projectors**

## Pin/Bump Description (continued)

| DI      | IN     |         |                                                                                                                                                                                              |                            |  |  |

|---------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|

| TQFN-EP | WLP    | NAME    | FUNCTION                                                                                                                                                                                     | EQUIVALENT INPUT SCHEMATIC |  |  |

| 23      | A2, A3 | OUT3    | Connection for Laser 3. Leave OUT3 unconnected if unused.                                                                                                                                    | LASER<br>OUTPUT            |  |  |

| 26      | A4, A5 | OUT2    | Connection for Laser 2. Leave OUT2 unconnected if unused.                                                                                                                                    |                            |  |  |

| 29      | A6, A7 | OUT1    | Connection for Laser 1. Leave OUT1 unconnected if unused.                                                                                                                                    | AGND =                     |  |  |

| 31      | C5     | EN_MAIN | Laser Enable Input with $100k\Omega$ Pulldown to DGND. Set EN_MAIN = high to enable OUT1-OUT3.                                                                                               | DVCC                       |  |  |

| 33      | B6     | MARKER  | Video Marker Input with 100kΩ Pullup to DVDD                                                                                                                                                 | DIGITAL INPUT              |  |  |

| 34      | C7     | DIO/SDA | SPI and I <sup>2</sup> C Serial Data Input/Output                                                                                                                                            |                            |  |  |

| 35      | D7     | CLK/SCL | SPI and I <sup>2</sup> C Serial Clock Input                                                                                                                                                  | DGND                       |  |  |

| 36      | D6     | CS      | SPI Chip Select with $100k\Omega$ Pulldown to DGND. Connect CS to DVDD for I <sup>2</sup> C mode. Set CS = low on power-up for SPI mode.                                                     | <del>'</del> =             |  |  |

| 39      | F7     | D0      | Synchronous Video Data Input, LSB                                                                                                                                                            | DVDD DIGITAL INPUT         |  |  |

| 40      | E6     | D1      | Synchronous Video Data Input                                                                                                                                                                 | DGND =                     |  |  |

| _       | _      | EP      | Exposed Pad (TQFN Only). EP is internally connected to DGND. The EP <b>must</b> be connected to the PCB ground plane through an array of vias for proper thermal and electrical performance. | _                          |  |  |

# **Laser Driver for Projectors**

### **Functional Diagram**

## **Laser Driver for Projectors**

### **Detailed Description**

The laser driver for projectors supports video imaging with red, blue, and green lasers. Each output includes two 8-bit video/offset DACs with programmable gain and offset.

#### **Video Demultiplexer**

The Video Demultiplexer supports three video formats and pixel clock configurations. The video format and demultiplexer are selected by the MUX select register (MS) as shown in <a href="Table 7">Table 7</a>.

#### Demux A

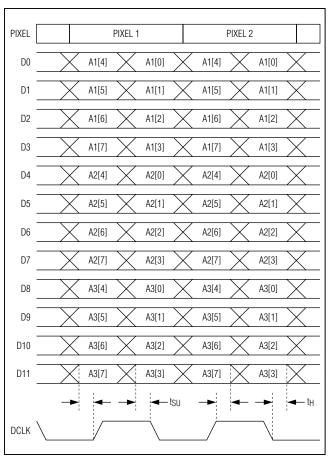

Demux A converts 4-bit input with DDR clock to 8-bit data with pixel clock. Input data must be formatted as shown in <u>Figure 5</u>. Four MSBs are latched on the rising edge of DCLK, and four LSBs are latched on the falling edge of DCLK.

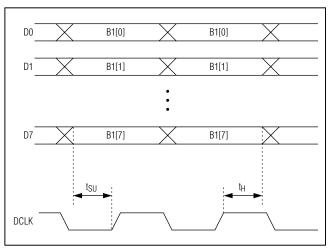

#### Demux B

Demux B latches an 8-bit video input on the rising edge of clock. The same video is sent to all outputs.

Figure 5. Video Demultiplexer A Input Waveform

Figure 6. Video Demultiplexer B Input Waveform

# **Laser Driver for Projectors**

Figure 7. Video C Demultiplexer Input Waveform

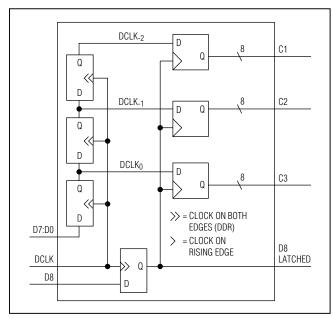

Figure 8. Video C Demultiplexer

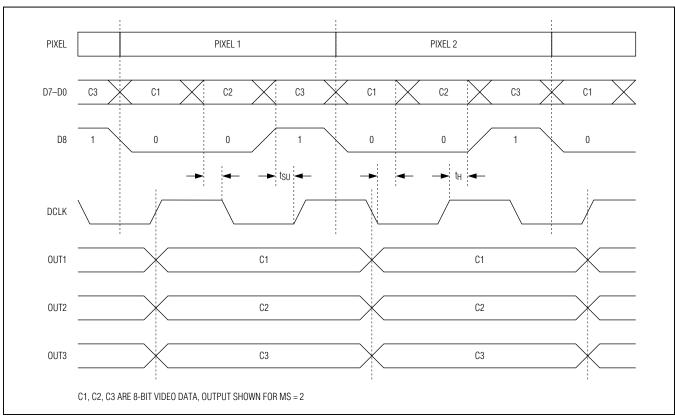

## Demux C

Demux C is compatible with the data format of the MAX3600. Data for the three outputs is multiplexed in time and uses a DDR clock.

# **Laser Driver for Projectors**

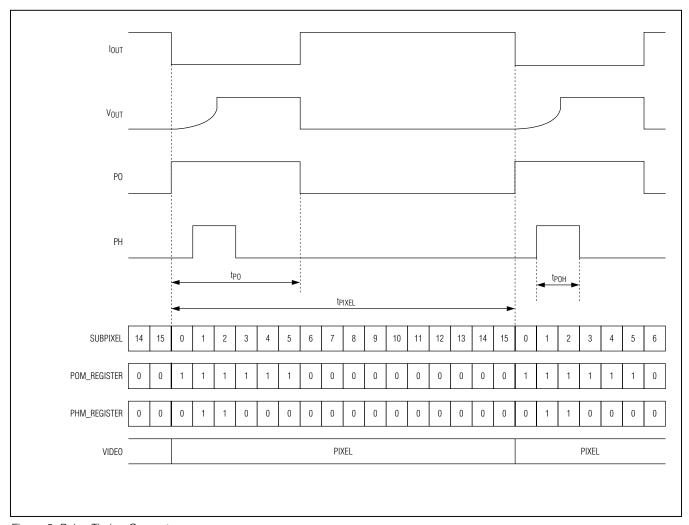

#### **Pulse Timing Generator**

The Pulse Timing generator creates phases of the pixel clock called subpixels (Figure 9). The subpixel timing signals enable laser current output pulsing for use with

despeckling the laser light. Each output of the laser driver can have different pulse widths or multiple pulses. If unused, disable the subpixel generator (D0 of register 0x0B) for additional power savings.

Figure 9. Pulse Timing Generator

# **Laser Driver for Projectors**

#### Subpixel Programming

The subpixel programming bits (D[2:0] of register 0x0C) determine the number of subpixels and duration of the pulse time (Table 1). The pulse width is applied to every pixel when the programmed pulse-off length > 0. This can be dynamically implemented to adjust for various lighting conditions.

#### Pulse-Off

The pulse-timing generator can be configured to skip pulse events to save power. The Pulse-Off Configuration

(POC) register selects options shown in <u>Table 2</u>. Random pulse-off events are triggered from a 31-bit pseudorandom bit-stream. By default, the PRBS is common to all outputs. Bit D4 of the POC\_registers determine which PRBS bits control each output (<u>Table 3</u>).

Pulse-off synchronization between outputs occurs when POC\_ registers match and POC\_[4] = 0. For example, if POC1 = POC2 = POC3 and POC\_[4] = 0, the occurrence of randomized pulse-off events at all outputs will be synchronized.

Table 1. Subpixel Programming (SP Register)

| CD   | f <sub>PIXEL</sub> | (MHz) | ACTIVE    | INACTIVE  |  |

|------|--------------------|-------|-----------|-----------|--|

| SP   | MIN                | MAX   | SUBPIXELS | SUBPIXELS |  |

| 000  | 150                | 200   | 0:7       | 8:15      |  |

| 001* | 75                 | 150   | 0:15      | _         |  |

| 010  | 50                 | 100   | 0:11      | 12;15     |  |

| 011  | 37.5               | 75    | 0:15      | _         |  |

| 100  | 30                 | 60    | 0:9       | 10:15     |  |

| 101  | 25                 | 50    | 0:15      | _         |  |

| 110  | 21.4               | 42.8  | 0:13      | 14:15     |  |

| 111  | 18.75              | 37.5  | 0:15      |           |  |

<sup>\*</sup>Power-on default

Table 2. Pulse-Off Duty Cycle (POC\_Register)

| POC_[3:0] | PULSE-OFF DUTY CYCLE   |

|-----------|------------------------|

| 0000*     | Every pixel, 100%      |

| 0001      | Random, 87.5%          |

| 0010      | Random, 75.0%          |

| 0011      | Random, 62.5%          |

| 0100      | Random, 50.0%          |

| 0101      | Random, 37.5%          |

| 0110      | Random, 25.0%          |

| 0111      | Random, 12.0%          |

| 1XXX      | Every other pixel, 50% |

<sup>\*</sup>Power-on default

**Table 3. Random Pulse-Off Programming**

| DOC [4] | PRBS31 BITS USED    |                     |                       |  |  |  |  |  |

|---------|---------------------|---------------------|-----------------------|--|--|--|--|--|

| POC_[4] | OUTPUT 1            | OUTPUT 2            | OUTPUT 3              |  |  |  |  |  |

| 0*      | PRBS31[4], [3], [0] | PRBS31[8], [7], [0] | PRBS31[16], [15], [0] |  |  |  |  |  |

| 1       | PRBS31[2:0]         | PRBS31[2:0]         | PRBS31[2:0]           |  |  |  |  |  |

<sup>\*</sup>Power-on default

# **Laser Driver for Projectors**

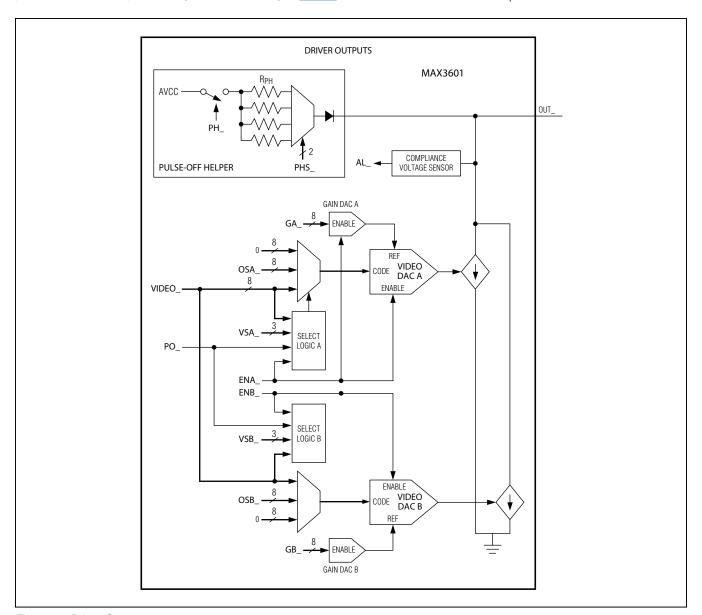

#### **Driver Outputs**

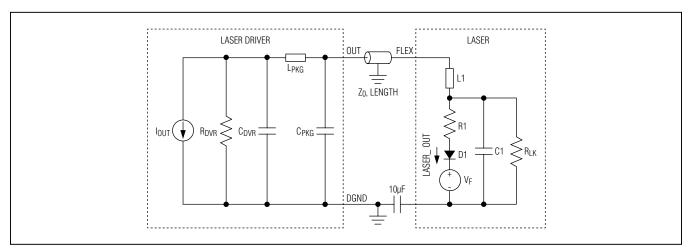

Each of the three laser driver outputs contains two video DACs, two gain DACs, a Compliance Voltage alarm, and Pulse-Off Assist. For power savings, the MAX3601 reduces supply current when outputs are not in use.

#### Video DACs

Each laser driver output contains two video DACs that produce current representing the video image (Figure

10). DACA has 4x the current output capability of DACB but is otherwise identical. Video Data is input from the high-speed data inputs. VSA\_ and VSB\_ determine the output behavior of the two video DACs (Table 4 and Table 5) The output video of either DAC can be any of the following:

- Video data

- Pulse-off with zero amplitude

Figure 10. Driver Output

Table 4. Video Select Logic for DAC A

| ENA_ | VSA_ | VIDEO | РО | CODE DAC A |

|------|------|-------|----|------------|

| 0    | X    | Χ     | X  | 0          |

|      | 000* | V     | 0  | VIDEO      |

|      | 000* | X     | 1  | 0          |

|      | 004  | V     | 0  | VIDEO      |

|      | 001  | X     | 1  | OSA_       |

|      | 040  | V     | 0  | OSA_       |

|      | 010  | X     | 1  | 0          |

| _    | 044  | V     | 0  | OSA_       |

| 1    | 011  | X     | 1  | OSA_       |

|      |      | 0     | Χ  | 0          |

|      | 100  |       | 0  | OSA_       |

|      |      | > 0   | 1  | 0          |

|      | 101  | Χ     | Χ  | 0          |

|      | 110  | Χ     | Χ  | 0          |

|      | 111  | Χ     | Χ  | 0          |

<sup>\*</sup>Power-on default

Table 5. Video Select Logic for DAC B

| ENB_ | VSB_ | VIDEO | РО | CODE DAC B |

|------|------|-------|----|------------|

| 0    | X    | Χ     | Χ  | 0          |

|      | 000* | V     | 0  | VIDEO      |

|      | 000* | X     | 1  | 0          |

|      | 001  | V     | 0  | VIDEO      |

|      | 001  | X     | 1  | OSB_       |

|      | 040  |       | 0  | OSB_       |

|      | 010  | X     | 1  | 0          |

| 1    | 044  | V     | 0  | OSB_       |

| '    | 011  | X     | 1  | OSB_       |

|      |      | 0     | Χ  | 0          |

|      | 100  |       | 0  | OSB_       |

|      |      | > 0   | 1  | 0          |

|      | 101  | Χ     | Χ  | 0          |

|      | 110  | Χ     | Χ  | 0          |

|      | 111  | X     | Х  | 0          |

<sup>\*</sup>Power-on default

- Pulse-off with non-zero amplitude

- · Constant value set from serial port

- Zero amplitude

- Constant for VIDEO > 0, zero when VIDEO = 0

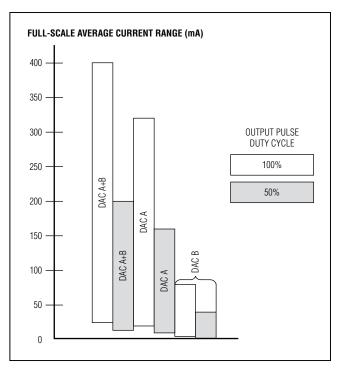

The two gain DACs adjust the full-scale output current for laser slope efficiency and color balance. Video Gain is programmed from the serial port. Full-scale output for Video DACs A and B are adjustable up to a peak output of 320mA and 80mA, respectively (Figure 11). The laser driver output current is the combined output of DAC A and B:

$$I_{OUT}(mA) = \frac{CODEA}{FFh} \left[ \frac{GA}{FFh} \right] \times 320 + \frac{CODEB}{FFh} \left[ \frac{GB}{FFh} \right] \times 80 + OSERR$$

where OSERR is the offset error.

Carefully consider the absolute maximum ratings of output current. If  $I_{OUT}$  is 400mA peak with 50% duty cycle over the life of the product, the average DC current is 200mA.

Figure 11. Driver Output Full-Scale Current Range

## **Laser Driver for Projectors**

Figure 12. Output Compliance Sensor

Figure 13. Example Use of Compliance Sensor

#### Pulse-Off and Pulse-off Assist

The Pulse feature rapidly pulses the laser off. The "off" level is set by the VSA\_ and VSB\_ registers (<u>Table 4</u>, <u>Table 5</u>).

Setting the PHM\_ register > 0 and setting either ENA\_ or ENB\_ high enables the pulse-off Assist circuit. In addition, the circuit is only active when MARKER is high and either output is enabled. During a pulse-off event, laser voltage is momentarily connected to 3.3V to improve turn-off time of slow lasers. Note that the pulse-off assist is only effective when the OSA\_ and OSB\_ registers are set to zero during pulse-off.

#### Compliance Voltage Sensor

The output voltage affects overshoot, settling time and linearity. The compliance alarm detects output voltage lower than a programmed threshold (Table 6) and sets the Compliance Alarm (VALM\_) bit (Figure 12). The alarm is cleared when read. The compliance alarm can be used to adjust laser power supplies after video data containing 50ns of bright pixels has been transmitted (Figure 13). The VALM bit will typically be set at power-on.

**Table 6. Compliance Alarm Setpoint**

| VSET_[3:0] | TYPICAL COMPLIANCE VOLTAGE THRESHOLD (V) |

|------------|------------------------------------------|

| 0000*      | 0.40                                     |

| 0001       | 0.48                                     |

| 0010       | 0.56                                     |

|            |                                          |

|            | •                                        |

| 1110       | 1.52                                     |

| 1111       | 1.60                                     |

<sup>\*</sup>Power-on default

# **Laser Driver for Projectors**

Figure 14. Temperature Alarm

Figure 15. Video Marker

# **Table 7. Video Demultiplexer Selection Logic**

| MS[2:0] | PIXEL<br>CLOCK<br>SOURCE | VIDEO 1 | VIDEO 2 | VIDEO 3 |  |  |  |  |

|---------|--------------------------|---------|---------|---------|--|--|--|--|

| 000*    | DCLK                     | A1      | A2      | А3      |  |  |  |  |

| 001     | DCLK                     | B1      | B1      | B1      |  |  |  |  |

| 010     | D8**                     | C1      | C2      | C3      |  |  |  |  |

| 011     | D8**                     | C2      | C2      | C2      |  |  |  |  |

| 100     | D8**                     | C2      | C2      | C3      |  |  |  |  |

| 101     | D8**                     | C2      | C3      | C3      |  |  |  |  |

| 110     | RESERVED                 |         |         |         |  |  |  |  |

| 111     | RESERVED                 |         |         |         |  |  |  |  |

<sup>\*</sup>Power-on default

#### **Temperature Alarm**

The temperature alarm reports if the driver temperature has exceeded a programmable threshold as shown in Figure 14. The alarm is cleared when the TALM register is read. If the die temperature is still above the threshold, the temperature alarm immediately re-asserts itself. The temperature threshold is programmed with the T\_SET register. The temperature alarm threshold includes offset of the temperature sensor. Accuracy of the threshold is increased by calibration of the alarm at a known temperature.

For example, if it is desired to set a temperature alarm at  $T_J=+125^{\circ}C$ : With  $T_A=+25^{\circ}C$  and outputs disabled, ramp TSET and read TALM. The code TSET $_{25}$ , where the alarm is set, corresponds to  $T_J\approx+25^{\circ}C$ . TSET $_{125}\approx$  TSET $_{25}+100^{\circ}C/2.5^{\circ}C/LSB$ .

#### **Control Logic**

The Control Logic provides video selection, laser enable, and power savings.

#### Video Selection

The video demultiplexers A, B, and C creates signals A1–A3, B1, and C1–C3. The MS bits select the input source video for VIDEO1, VIDEO2, and VIDEO3.

#### Laser Control

When EN\_MAIN is low, all drivers are off. This signal works asynchronously (no clock is required to disable outputs).

The Video Marker (MARKER) input can be used to disable selected outputs when a video signal is not present (Figure 15). The VE[1:3] bit settings determine which outputs respond to the MARKER signal.

<sup>\*\*</sup>D8 is gated by DCLK

## **Laser Driver for Projectors**

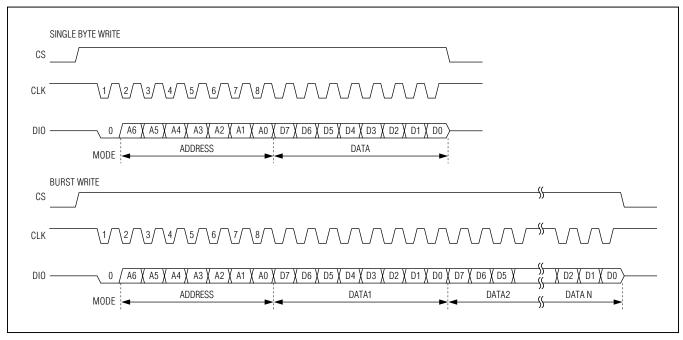

### **Serial Port and Registers**

The MAX3601 contains an I<sup>2</sup>C interface and a 3-wire SPI interface. The communication mode is determined by the state of CS at power-on. If CS is high (tied to DVDD), I<sup>2</sup>C mode is selected. If CS is open or low at power-on, SPI mode is selected.

#### I<sup>2</sup>C Interface

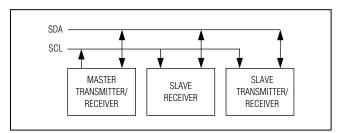

The serial bus consists of a bidirectional serial-data line (SDA) and a serial-clock input (SCL). The master generates the clock signal (Figure 16).

$I^2C$  is an open-drain bus. SDA and SCL require pullup resistors (500 $\Omega$  or greater). Voltage clamps on the input protect the device high-voltage spikes not exceeding the absolute maximum voltage rating.

#### Data Transfer

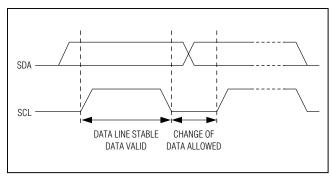

One data bit is transferred during each SCL clock cycle. The data on SDA must remain stable during the high

Figure 16. I<sup>2</sup>C Master/Slave Configuration

Figure 17. I<sup>2</sup>C Bit Transfer

period of the SCL clock pulse (<u>Figure 17</u>). Changes in SDA while SCL is high are control signals (see the <u>START</u> and <u>STOP Conditions</u> section for more information).

Each transmit sequence is framed by a START (S) condition and a STOP (P) condition. Each data packet is 9 bits long; 8 bits of data followed by the acknowledge bit

#### START and STOP Conditions

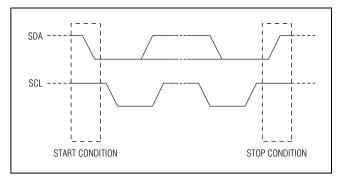

When the serial interface is inactive, SDA and SCL idle high. A master device initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA, while SCL is high (Figure 18).

A START condition from the master signals the beginning of a transmission. The master terminates transmission by issuing a not-acknowledge followed by a STOP condition (see Figure 19 for more information). The STOP condition frees the bus. To issue a series of commands to the slave, the master may issue repeated START (Sr) commands instead of a STOP command in order to maintain control of the bus. In general, a repeated START command is functionally equivalent to a regular START command.

When a STOP condition or incorrect address is detected, the MAX3601 internally disconnects SCL from the serial interface until the next START condition, minimizing digital noise and feedthrough.

Figure 18. I<sup>2</sup>C START and STOP Conditions

## **Laser Driver for Projectors**

#### Acknowledge

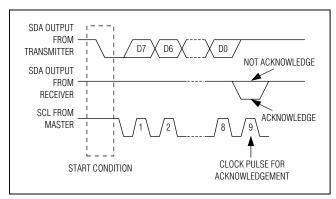

Both the master and the MAX3601 (slave) generate acknowledge bits when receiving data. The acknowledge bit is the last bit of each 9-bit data packet (Figure 19). To generate an acknowledge (A), the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (ninth pulse) and keep it low during the high period of the clock pulse. To generate a not acknowledge (NA), the receiving device allows SDA to be pulled high before the rising edge of the acknowledge-related clock pulse and leaves it high during the high period of the clock pulse.