# SYSMAC C1000H/C2000H Programmable Controllers

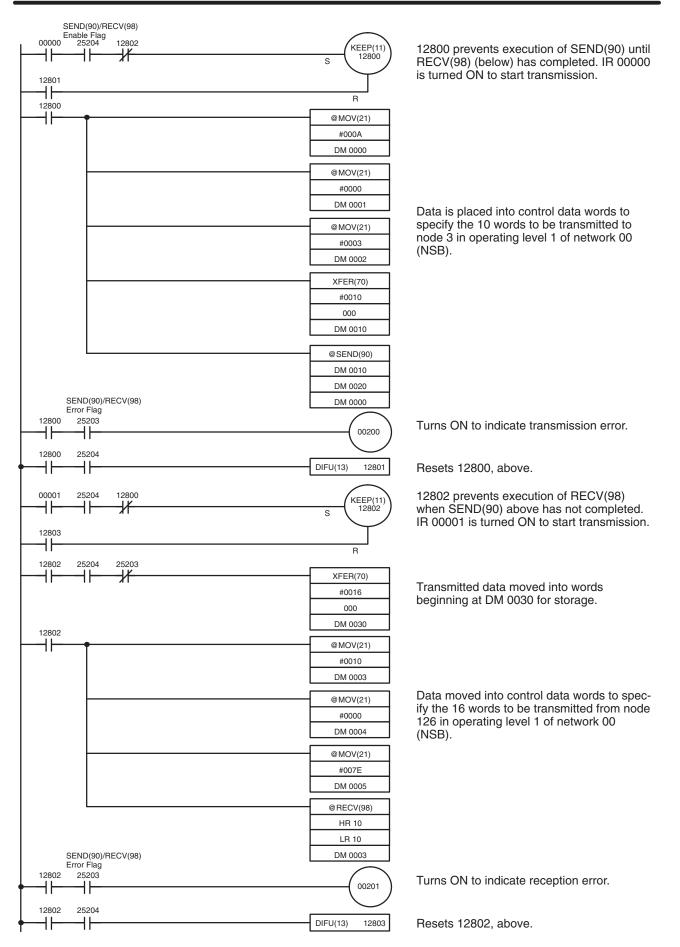

# **OPERATION MANUAL**

# C1000H/C2000H Programmable Controllers

## **Operation Manual**

Revised May 2003

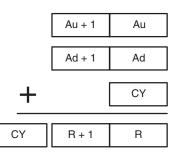

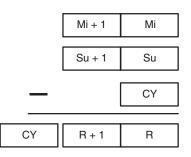

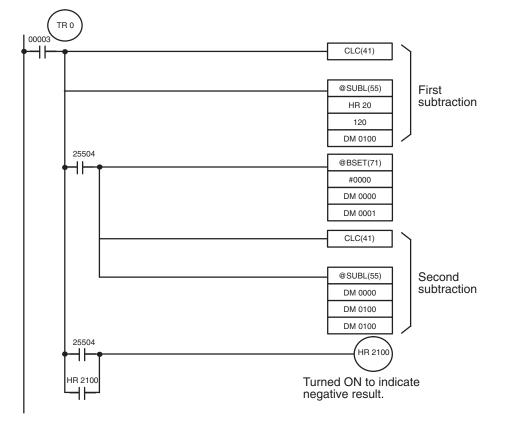

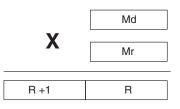

### Certain Terms and Conditions of Sale

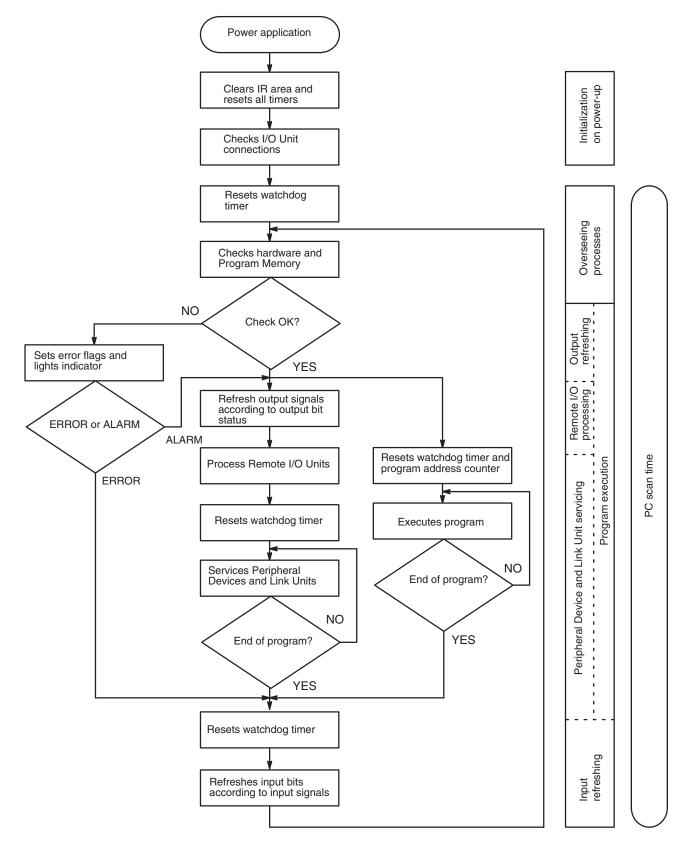

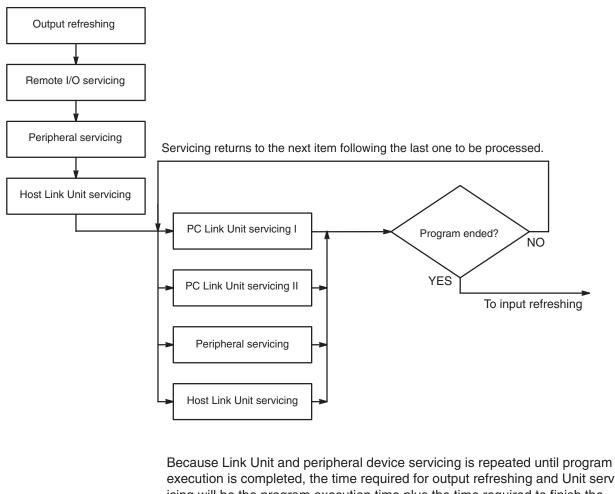

- <u>Offer; Acceptance.</u> These terms and conditions (these "<u>Terms</u>") are deemed part of all catalogs, manuals or other documents, whether electronic or in writing, relating to the sale of goods or services (collectively, the "<u>Goods</u>") by Omron Electronics LLC and its subsidiary companies ("<u>Seller</u>"). Seller hereby objects to any terms or conditions proposed in Buyer's purchase order or other documents which are inconsistent with, or in addition to, these Terms. Please contact your Omron representative to confirm any additional terms for sales from your Omron company

- 2

- trom your Omron company. <u>Prices.</u> All prices stated are current, subject to change without notice by Seller. Buyer agrees to pay the price in effect at time of shipment. <u>Discounts.</u> Cash discounts, if any, will apply only on the net amount of invoices sent to Buyer after deducting transportation charges, taxes and duties, and will be allowed only if (i) the invoice is paid according to Seller's payment terms and (ii) Buyer has no past due amounts owing to Seller. <u>Orders.</u> Seller will accept no order less than \$200 net billing. 3.

- Governmental Approvals. Buyer shall be responsible for, and shall bear all costs involved in, obtaining any government approvals required for the impor-5 tation or sale of the Goods.

- Taxes. All taxes, duties and other governmental charges (other than general real property and income taxes), including any interest or penalties thereon, imposed directly or indirectly on Seller or required to be collected directly or indirectly by Seller for the manufacture, production, sale, delivery, importation, consumption or use of the Goods sold hereunder (including customs duties and ealing available) applies and the program of the Goods and the other customs duties and ealing available. 6. and sales, excise, use, turnover and license taxes) shall be charged to and remitted by Buyer to Seller.

- Financial. If the financial position of Buyer at any time becomes unsatisfactory to Seller, Seller reserves the right to stop shipments or require satisfactory security or payment in advance. If Buyer fails to make payment or otherwise comply with these Terms or any related agreement, Seller may (without liability and in addition to other remedies) cancel any unshipped portion of Goods sold hereunder and stop any Goods in transit until Buyer pays all amounts, includ-ing amounts payable hereunder, whether or not then due, which are owing to it by Buyer. Buyer shall in any event remain liable for all unpaid accounts.

- Cancellation; Etc. Orders are not subject to rescheduling or cancellation unless Buyer indemnifies Seller fully against all costs or expenses arising in 8. connection therewith.

- connection therewith.

Force Majeure. Seller shall not be liable for any delay or failure in delivery resulting from causes beyond its control, including earthquakes, fires, floods, strikes or other labor disputes, shortage of labor or materials, accidents to machinery, acts of sabotage, riots, delay in or lack of transportation or the requirements of any government authority.

Shipping: Delivery. Unless otherwise expressly agreed in writing by Seller:

a. Shipments shall be by a carrier selected by Seller;

b. Such carrier shall act as the agent of Buyer and delivery to such carrier shall constitute delivery to Buyer;

c. All sales and shipments of Goods shall be FOB shipping point (unless otherwise stated in writing by Seller), at which point title to and all risk of loss of the Goods shall pass from Seller to Buyer, provided that Seller shall retain a security interest in the Goods until the full purchase price is paid by Buyer;

- - d. Delivery and shipping dates are estimates only.e. Seller will package Goods as it deems proper for protection against normal

- belief win package Goods as in deems proper for protection against normal handling and extra charges apply to special conditions.

<u>Claims</u>. Any claim by Buyer against Seller for shortage or damage to the Goods occurring before delivery to the carrier must be presented in writing to Seller within 30 days of receipt of shipment and include the original transportation bill signed by the carrier noting that the carrier received the Goods from Seller in the condition disinged. Seller in the condition claimed.

- <u>Warranties.</u> (a) <u>Exclusive Warranty.</u> Seller's exclusive warranty is that the Goods will be free from defects in materials and workmanship for a period of Goods will be free from defects in materials and workmanship for a period of twelve months from the date of sale by Seller (or such other period expressed in writing by Seller). Seller disclaims all other warranties, express or implied. (b) <u>Limitations</u>. SELLER MAKES NO WARRANTY OR REPRESENTATION, EXPRESS OR IMPLIED, ABOUT NON-INFRINGEMENT, MERCHANTABIL-ITY OR FITNESS FOR A PARTICULAR PURPOSE OF THE GOODS. BUYER ACKNOWLEDGES THAT IT ALONE HAS DETERMINED THAT THE GOODS WILL SUITABLY MEET THE REQUIREMENTS OF THEIR INTENDED USE. Seller further disclaims all warranties and responsibility of any type for claims or expresses based on infringement by the Goods or other-INTENDED USE. Seller further disclaims all warranties and responsibility of any type for claims or expenses based on infringement by the Goods or other-wise of any intellectual property right. (c) <u>Buyer Remedy</u>. Seller's sole obliga-tion hereunder shall be to replace (in the form originally shipped with Buyer responsible for labor charges for removal or replacement thereof) the non-complying Good or, at Seller's election, to repay or credit Buyer an amount equal to the purchase price of the Good; provided that in no event shall Seller be responsible for warranty, repair, indemnity or any other claims or expenses regarding the Goods unless Seller's analysis confirms that the Goods were properly handled, stored, installed and maintained and not subject to contami-nation, abuse, misuse or inappropriate modification. Return of any goods by Buyer must be approved in writing by Seller before shipment. Seller shall not be liable for the suitability or the results from the use of Goods in combination with any electrical or electronic components, circuits, system assemblies or any other materials or substances or environments. Any advice, recommendations or information given orally or in writing, are not to be construed as an amendment or addition to the above warranty.

- advice, recommendations or information given orally or in writing, are not to be construed as an amendment or addition to the above warranty. <u>Damage Limits: Etc.</u> SELLER SHALL NOT BE LIABLE FOR SPECIAL, INDI-RECT OR CONSEQUENTIAL DAMAGES, LOSS OF PROFITS OR PRODUC-TION OR COMMERCIAL LOSS IN ANY WAY CONNECTED WITH THE GOODS, WHETHER SUCH CLAIM IS BASED IN CONTRACT, WARRANTY, NEGLIGENCE OR STRICT LIABILITY. Further, in no event shall liability of Seller exceed the individual price of the Good on which liability is asserted. Indemnities. Buyer shall indemnify and hold harmless Seller, its affiliates and its employees from and against all liabilities, losses, claims, costs and expenses (including attorney's fees and expenses) related to any claim, inves-tigation, litigation or proceeding (whether or not Seller is a party) which arises or is alleged to arise from Buyer's acts or omissions under these Terms or in 13.

- or is alleged to arise from Buyer's acts or omissions under these Terms or in any way with respect to the Goods. Without limiting the foregoing, Buyer (at its own expense) shall indemnify and hold harmless Seller and defend or settle any action brought against Seller to the extent that it is based on a claim that any Good made to Buyer specifications infringed intellectual property rights of

- 15

- any Good made to Buyer specifications infringed intellectual property rights of another party.

Property: Confidentiality. The intellectual property embodied in the Goods is the exclusive property of Seller and its affiliates and Buyer shall not attempt to duplicate it in any way without the written permission of Seller. Notwithstanding any charges to Buyer for engineering or tooling, all engineering and tooling shall remain the exclusive property of Seller. All information and materials supplied by Seller to Buyer relating to the Goods are confidential and proprietary, and Buyer shall limit distribution thereof to its trusted employees and strictly prevent disclosure to any third party.

Miscellaneous. (a) Waiver. No failure or delay by Seller in exercising any right and no course of dealing between Buyer and Seller shall operate as a waiver of rights by Seller. (b) Assignment. Buyer may not assign its rights hereunder without Seller's written consent. (c) Amendment. These Terms constitute the entire agreement between Buyer and Seller relating to the Goods, and no provision shall not invalidate any other provision. (e) Setoff. Buyer shall have no right to set off any amounts against the amount owing in respect of this invoice. (f) As used herein, "including" means "including without limitation".

#### Certain Precautions on Specifications and Use

- Suitability of Use. Seller shall not be responsible for conformity with any standards, codes or regulations which apply to the combination of the Good in the Buyer's application or use of the Good. At Buyer's request, Seller will provide Buyer's application or use of the Good. At Buyer's request, Seller Will provide applicable third party certification documents identifying ratings and limitations of use which apply to the Good. This information by itself is not sufficient for a complete determination of the suitability of the Good in combination with the end product, machine, system, or other application or use. The following are some examples of applications for which particular attention must be given. This is not intended to be an exhaustive list of all possible uses of this Good; nor is it intended to imply that the uses listed may be suitable for this Good: (i). Outdoor use, uses involving optential chemical contamination or electrical

- Outdoor use, uses involving potential chemical contamination or electrical interference, or conditions or uses not described in this document.

- (ii) Energy control systems, combustion systems, railroad systems, aviation systems, medical equipment, amusement machines, vehicles, safety equipment, and installations subject to separate industry or government regulations

- (iii) Systems, machines and equipment that could present a risk to life or property. Please know and observe all prohibitions of use applicable to

THE SELLER'S PRODUCT SOLVERALL FOURPENT OF SYSTEM THE INTENDED USE WITHIN THE OVERALL EQUIPMENT OR SYSTEM.

- 3

- Programmable Products. Seller shall not be responsible for the user's pro-gramming of a programmable Good, or any consequence thereof. <u>Performance Data</u>. Performance data given in this catalog is provided as a guide for the user in determining suitability and does not constitute a warranty. It may represent the result of Seller's test conditions, and the user must corre-late it to actual application requirements. Actual performance is subject to the Seller's Warranty and Limitations of Liability. <u>Change in Specifications</u>. Product specifications and accessories may be changed at any time based on improvements and other reasons. It is our prac-tice to change part numbers when published ratings or features are changed, or when significant construction changes are made. However, some specifica-tions of the Good may be changed without any notice. When in doubt, special part numbers may be assigned to fix or establish key specifications for your application. Please consult with your Seller's representative at any time to con-

- application. Please consult with your Seller's representative at any time to con-firm actual specifications of purchased Good. <u>Errors and Omissions</u>. The information in this catalog has been carefully checked and is believed to be accurate; however, no responsibility is assumed for clerical, typographical or proofreading errors, or omissions. 5.

#### Notice:

OMRON products are manufactured for use according to proper procedures by a qualified operator and only for the purposes described in this manual.

The following conventions are used to indicate and classify precautions in this manual. Always heed the information provided with them. Failure to heed precautions can result in injury to people or damage to the product.

**Caution** Indicates information that, if not heeded, could result in relatively serious or minor injury, damage to the product, or faulty operation.

#### **OMRON Product References**

All OMRON products are capitalized in this manual. The word "Unit" is also capitalized when it refers to an OMRON product, regardless of whether or not it appears in the proper name of the product.

The abbreviation "Ch," which appears in some displays and on some OMRON products, means "word" and is abbreviated "Wd" in documentation.

The abbreviation "PC" means Programmable Controller and is not used as an abbreviation for anything else.

#### Visual Aids

The following headings appear in the left column of the manual to help you locate different types of information.

**Note** Indicates information of particular interest for efficient and convenient operation of the product.

1, 2, 3... Indicates lists of one sort or another, such as procedures, precautions, etc.

#### © OMRON, 1990

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or by any means, mechanical, electronic, photocopying, recording, or otherwise, without the prior written permission of OMRON.

No patent liability is assumed with respect to the use of the information contained herein. Moreover, because OMRON is constantly striving to improve its high-quality products, the information contained in this manual is subject to change without notice. Every precaution has been taken in the preparation of this manual. Nevertheless, OMRON assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained in this publication.

## **TABLE OF CONTENTS**

| SEC                                           | TION 1                                                                                                                                          |                                 |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Intro                                         | oduction                                                                                                                                        | 1                               |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7 | OverviewRelay Circuits: The Roots of PC LogicPC TerminologyOMRON Product TerminologyOverview of PC OperationPeripheral DevicesAvailable Manuals | 2<br>2<br>3<br>4<br>4<br>5<br>7 |

| SEC                                           | TION 2                                                                                                                                          |                                 |

|                                               | dware Considerations                                                                                                                            | 9                               |

| 2-1                                           | Indicators                                                                                                                                      | -                               |

| 2-1                                           | PC Configuration                                                                                                                                | 10<br>12                        |

|                                               |                                                                                                                                                 | 12                              |

| SEC                                           | TION 3                                                                                                                                          |                                 |

| Men                                           | nory Areas                                                                                                                                      | 15                              |

| 3-1                                           | Introduction                                                                                                                                    | 16                              |

| 3-2                                           | Data Area Structure                                                                                                                             | 16                              |

| 3-3                                           | IR (Internal Relay)Area                                                                                                                         | 18                              |

| 3-4                                           | SR (Special Relay) Area                                                                                                                         | 23                              |

| 3-5                                           | AR (Auxiliary Relay) Area                                                                                                                       | 31                              |

| 3-6                                           | DM (Data Memory) Area                                                                                                                           | 36                              |

| 3-7                                           | HR (Holding Relay) Area                                                                                                                         | 37                              |

| 3-8                                           | TC (Timer/Counter) Area                                                                                                                         | 37                              |

| 3-9                                           | LR (Link Relay) Area                                                                                                                            | 38                              |

|                                               | Program Memory                                                                                                                                  | 39                              |

| 3-11                                          | · · · · · · · · · · · · · · · · · · ·                                                                                                           | 39                              |

| 3-12                                          | ······································                                                                                                          | 39<br>39                        |

|                                               | TR (Temporary Relay) Area                                                                                                                       | 53                              |

| SEC                                           | TION 4                                                                                                                                          |                                 |

| Writ                                          | ting and Inputting the Program                                                                                                                  | 41                              |

|                                               | Basic Procedure                                                                                                                                 | 42                              |

| 4-2                                           | Instruction Terminology                                                                                                                         | 42                              |

| 4-3                                           | Basic Ladder Diagrams                                                                                                                           | 43                              |

| 4-4                                           | The Programming Console                                                                                                                         | 58                              |

| 4-5                                           | Preparation for Operation                                                                                                                       | 6                               |

| 4-6                                           | Inputting, Modifying, and Checking the Program                                                                                                  | 7                               |

| 4-7                                           | Controlling Bit Status                                                                                                                          | 92                              |

| 4-8                                           | Work Bits (Internal Relays)                                                                                                                     | 9                               |

| 4-9                                           | Programming Precautions                                                                                                                         | 9:                              |

| 4-10                                          | Program Execution                                                                                                                               | 9                               |

#### **SECTION 5 Instruction S**

| Instr | ruction Set                                        | 99  |  |  |

|-------|----------------------------------------------------|-----|--|--|

| 5-1   | Notation                                           | 102 |  |  |

| 5-2   | Instruction Format                                 | 102 |  |  |

| 5-3   | Data Areas, Definer Values, and Flags              | 102 |  |  |

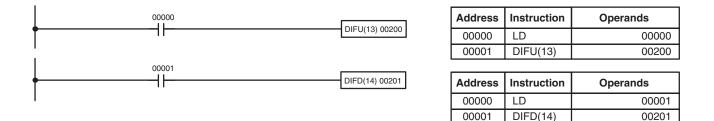

| 5-4   | Differentiated Instructions                        |     |  |  |

| 5-5   | Coding Right-hand Instructions                     | 104 |  |  |

| 5-6   | Ladder Diagram Instructions                        | 107 |  |  |

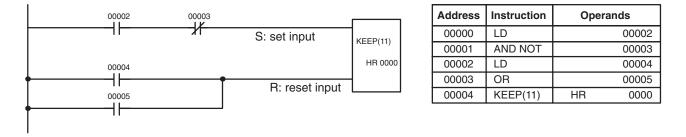

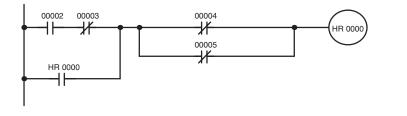

| 5-7   | Bit Control Instructions                           | 109 |  |  |

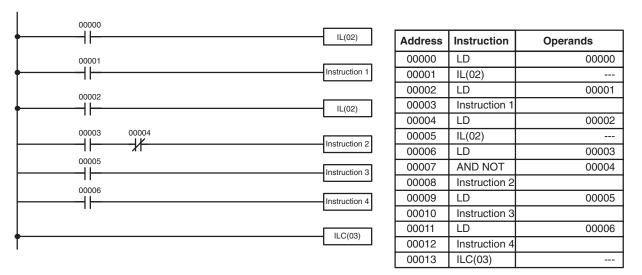

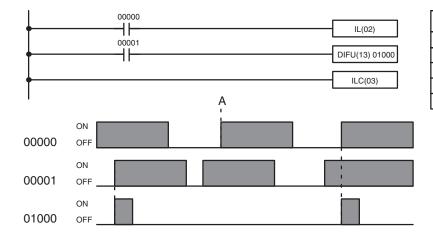

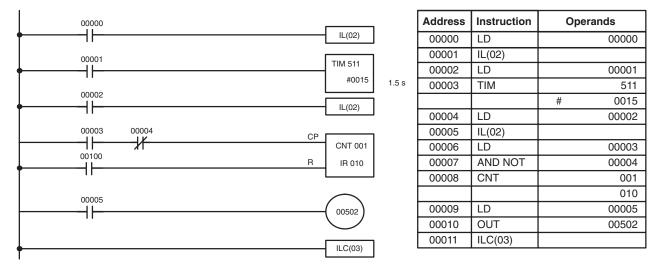

| 5-8   | INTERLOCK and INTERLOCK CLEAR – IL(02) and ILC(03) | 113 |  |  |

| 5-9   | JUMP and JUMP END – JMP(04) and JME(05)            | 115 |  |  |

| 5-10  | END – END(01)                                      | 116 |  |  |

| 5-11  | NO OPERATION – NOP(00)                             | 116 |  |  |

| 5-12  | Timer and Counter Instructions                     | 117 |  |  |

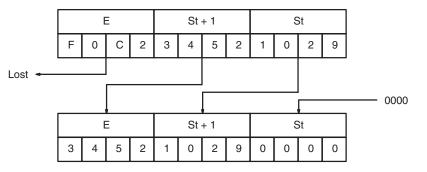

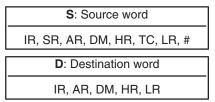

| 5-13  | Data Shifting                                      | 127 |  |  |

| 5-14  | Data Movement                                      | 135 |  |  |

| 5-15  | Data Comparison                                    | 142 |  |  |

| 5-16  | Data Conversion                                    | 148 |  |  |

| 5-17  | BCD Calculations                                   | 158 |  |  |

| 5-18  | Binary Calculations                                | 174 |  |  |

| 5-19  | Logic Instructions                                 | 179 |  |  |

| 5-20  | Subroutines and Interrupt Control                  | 182 |  |  |

|       | Block Programming Instructions                     | 190 |  |  |

| 5-22  | Step Instructions                                  | 199 |  |  |

|       | Special Instructions                               | 208 |  |  |

| 5-24  | Data Tracing (TRACE MEMORY SAMPLING – TRSM(45))    | 211 |  |  |

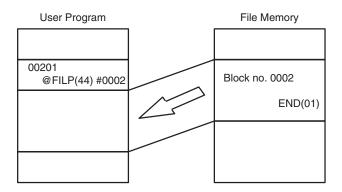

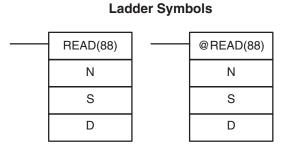

| 5-25  | File Memory Instructions                           | 214 |  |  |

|       | Intelligent I/O Instructions                       | 217 |  |  |

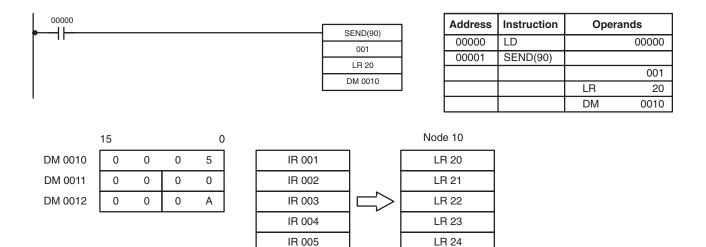

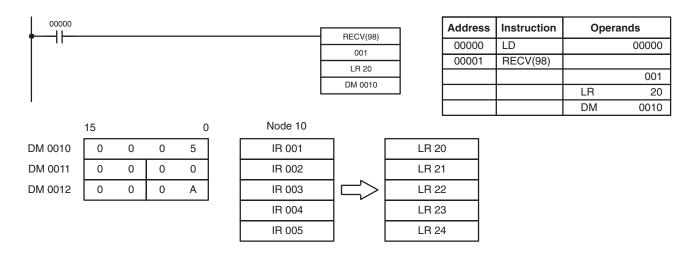

| 5-27  | Network Instructions                               | 219 |  |  |

| SEC   | TION 6                                             |     |  |  |

| Prog  | ram Execution Timing                               | 227 |  |  |

| 6-1   | Cycle Time                                         | 228 |  |  |

| 6-2   | Calculating Cycle Time                             | 232 |  |  |

| 6-3   | Instruction Execution Times                        | 235 |  |  |

| 6-4   | I/O Response Time                                  | 241 |  |  |

| SEC   | TION 7                                             |     |  |  |

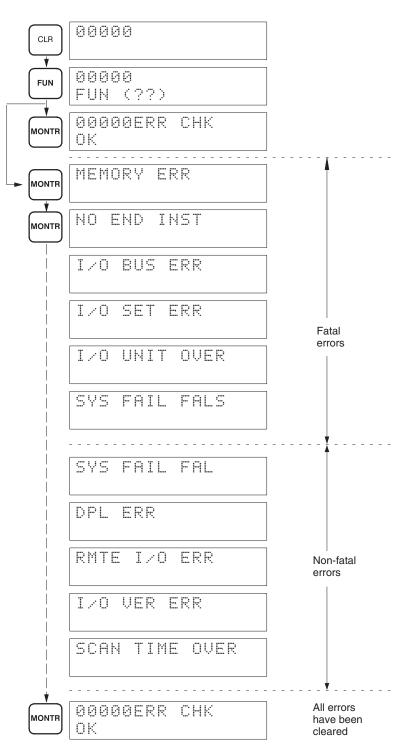

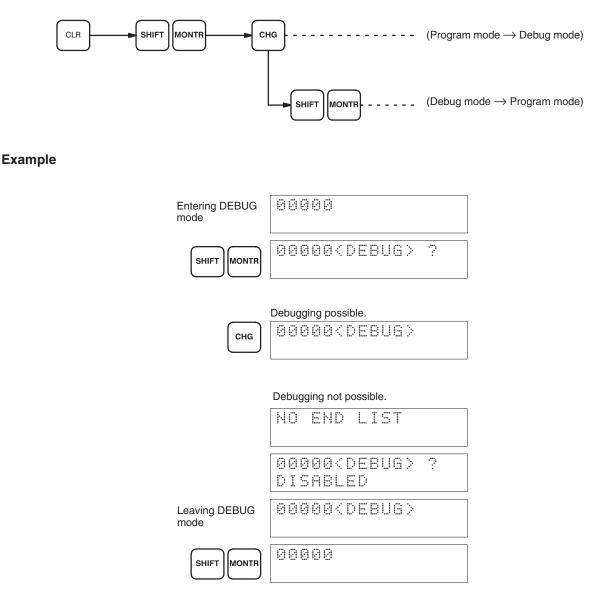

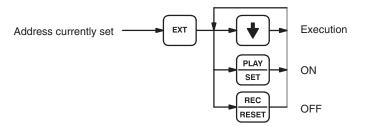

| Prog  | ram Debugging and Execution                        | 243 |  |  |

| ~8    |                                                    |     |  |  |

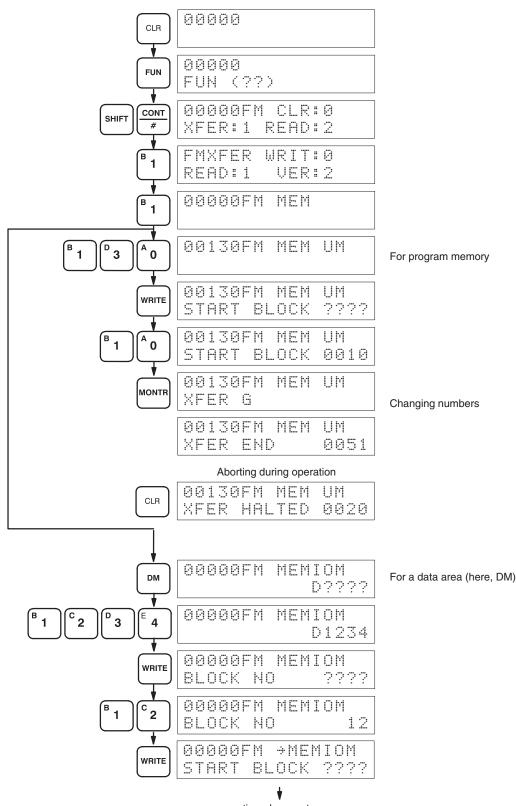

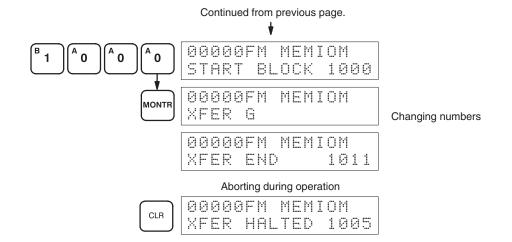

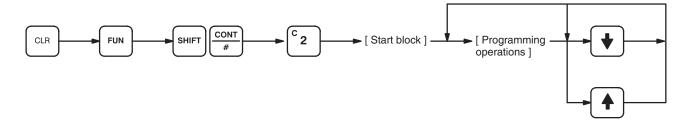

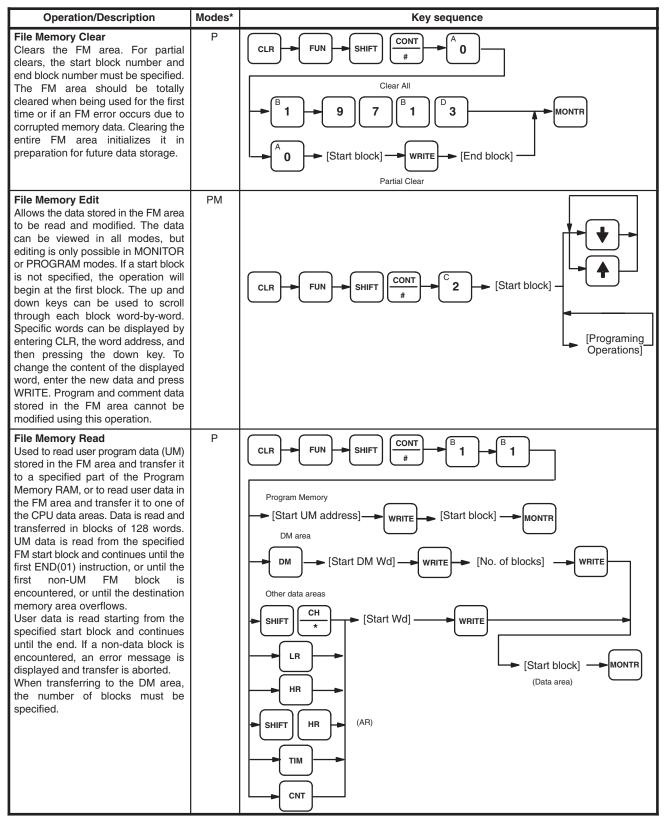

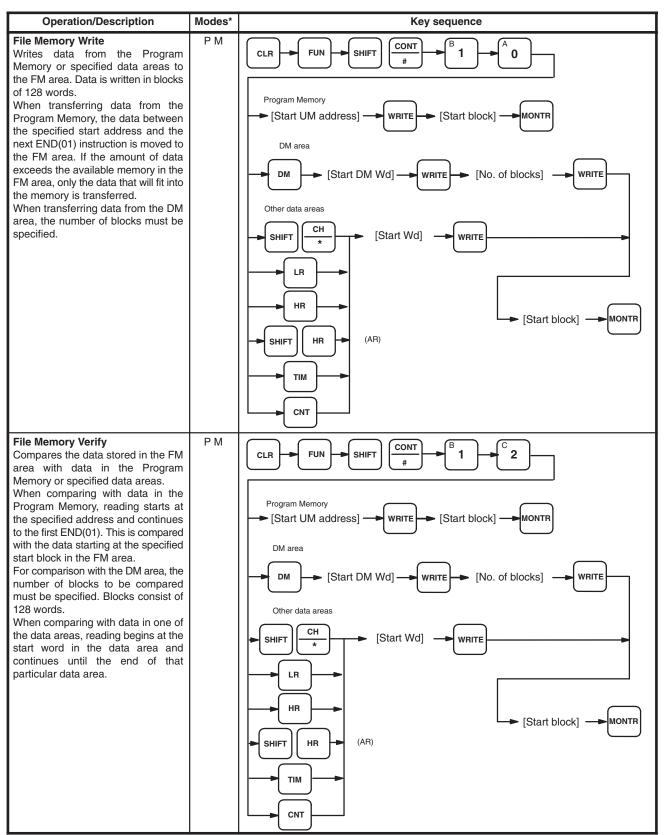

7-1Debugging2447-2Monitoring Operation and Modifying Data2527-3File Memory Operations2667-4Program Backup and Restore Operations276

#### **SECTION 8**

| Erro | or Processing 2                          |

|------|------------------------------------------|

| 8-1  | Alarm Indicators                         |

| 8-2  | Programmed Alarms and Error Messages     |

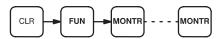

| 8-3  | Reading and Clearing Errors and Messages |

| 8-4  | Error Messages                           |

| 8-5  | Error Flags                              |

| 8-6  | Troubleshooting                          |

| Арр  | endices                                  |

| Ā.   | Standard Models                          |

| В.   | Programming Instructions                 |

| C.   | Programming Console Operations           |

| D.   | Error and Arithmetic Flag Operation      |

| E.   | Data Areas                               |

| F.   | I/O Assignment Records Sheets            |

| G.   | Program Coding Sheet                     |

| H.   | Data Conversion Table                    |

| I.   | Extended ASCII                           |

| Glos | sary 3                                   |

| Inde | ex                                       |

| Revi | sion History                             |

#### About this Manual:

The OMRON C1000H and C2000H offer an effective way to automate processing. Manufacturing, assembly, packaging, and many other processes can be automated to save time and money. Distributed control systems can also be designed to allow centralized monitoring and supervision of several separate controlled systems. Monitoring and supervising can be done through a host computer, connecting the controlled system to a data bank. It is thus possible to have adjustments in system operation made automatically to compensate for requirement changes.

The C1000H and C2000H are Rack PCs, i.e., various Units are combined to produce the optimum control system for each application, which can just as easily be expanded up to the maximum I/O capacity of the PC by adding additional Units in the future. Additional Units include dedicated Special I/O Units that can be used for specific tacks and Link Units that can be used to build more highly integrated systems, including an optical LAN.

The C1000H and C2000H are equipped with large programming instruction sets, data areas, and other features to control processing directly or remotely. Programming utilizes ladder-diagram programming methods, which are described in detail for those unfamiliar with them.

This manual describes the characteristics and abilities of the C1000H and C2000H, programming operations and instructions, and other aspects of operation and preparation that demand attention. Before attempting to operate the PC, thoroughly familiarize yourself with the information contained herein. Hardware information is provided in detail in the *C1000H/C2000H Installation Guide*. A table of other manuals that can be used in combination with this manual is provided at the end of *Section 1 Introduction*.

**Section 1 Introduction** explains the background and some of the basic terms used in ladder-diagram programming. It also provides an overview of the process of programming and operating a PC and explains basic terminology used with OMRON PCs. Descriptions of peripheral devices used with the C1000H and C2000H and a table of other manuals available to use with this manual for special PC applications are also provided.

**Section 2 Hardware Considerations** explains basic aspects of the overall PC configuration and describes the indicators that are referred to in other sections of this manual.

**Section 3 Memory Areas** takes a look at the way memory is divided and allocated and explains the information provided there to aid in programming. It also explains how I/O is managed in memory and how bits in memory correspond to specific I/O points.

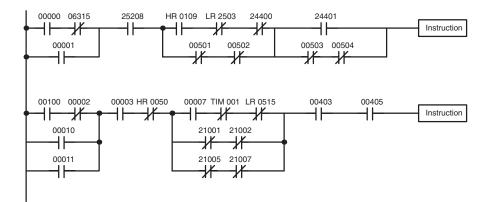

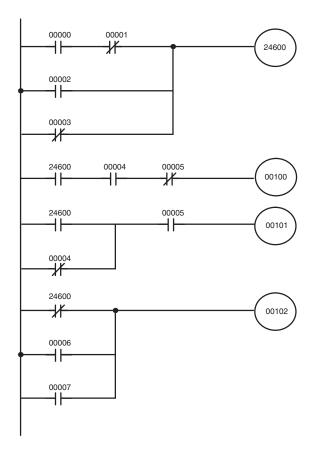

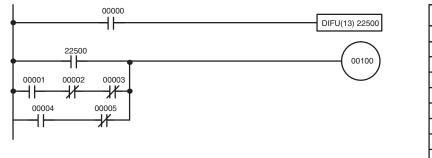

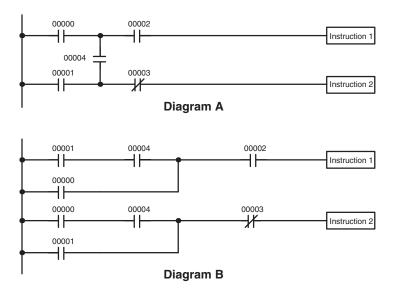

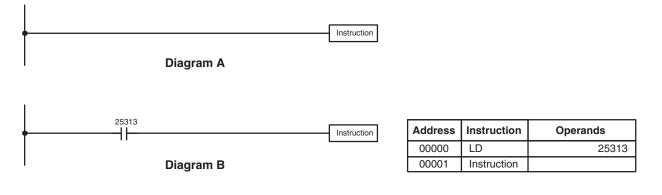

**Section 4 Writing and Inputting the Programming** explains the basics of ladder-diagram programming and how the program is input into the PC using a Programming Console. The elements that make up the 'ladder' part of a ladder-diagram program and how execution of this program is controlled are explained. The user should be able to write and input a basic "input-output" program after finishing this section.

Section 5 Instruction Set then goes on to describe individually all of the instructions used in programming.

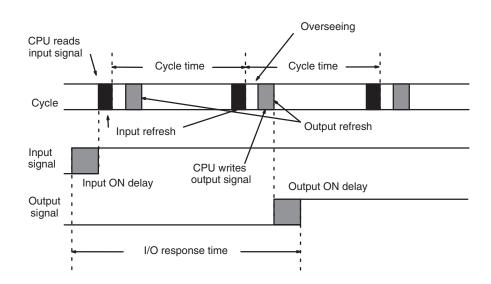

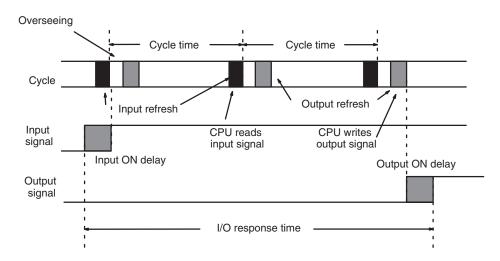

*Section 6 Program Execution Timing* explains the cycling process used to execute the program and tells how to coordinate inputs and outputs so that they occur at the proper times.

*Section 7 Program Debugging and Execution* provides the Programming Console procedures used to debug the program and to monitor and control operation.

Finally, *Section 8 Troubleshooting* provides information on error indications and other means of reducing down time. Information in this section is also sometimes necessary when debugging a program.

The appendices provide tables of standard OMRON products available for the C1000H and C2000H, reference tables of instructions and Programming Console operations, and other information helpful in PC operation.

# **WARNING** Failure to read and understand the information provided in this manual may result in personal injury or death, damage to the product, or product failure. Please read each section in its entirety and be sure you understand the information provided in the section and related sections before attempting any of the procedures or operations given.

#### **SECTION 1 Introduction**

This section gives a brief overview of the history of Programmable Controllers and explains terms commonly used in ladder-diagram programming. It also provides an overview of the process of programming and operating a PC and explains basic terminology used with OMRON PCs. Descriptions of peripheral devices used with the C1000H and C2000H, and a table of other manuals available to use with this manual for special PC applications, are also provided.

| 1-1 | Overview                              | 2 |

|-----|---------------------------------------|---|

| 1-2 | Relay Circuits: The Roots of PC Logic | 2 |

| 1-3 | PC Terminology                        | 3 |

| 1-4 | OMRON Product Terminology             | 4 |

| 1-5 | Overview of PC Operation              | 4 |

| 1-6 | Peripheral Devices                    | 5 |

| 1-7 | Available Manuals                     | 7 |

#### 1-1 Overview

A PC (Programmable Controller) is basically a CPU (Central Processing Unit) containing a program and connected to input and output (I/O) devices. The program controls the PC so that when an input signal from an input device turns ON, the appropriate response is made. The response normally involves turning ON an output signal to some sort of output device. The input devices could be photoelectric sensors, pushbuttons on control panels, limit switches, or any other devices that can produce a signal that can be input into the PC. The output devices could be solenoids, switches activating indicator lamps, relays turning on motors, or any other devices that can be activated by signals output from the PC.

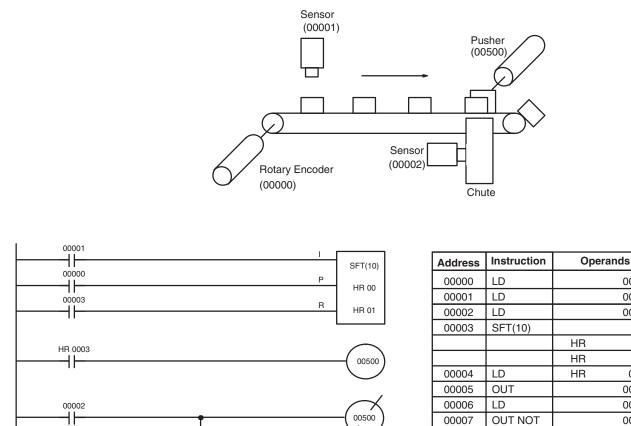

For example, a sensor detecting a passing product turns ON an input to the PC. The PC responds by turning ON an output that activates a pusher that pushes the product onto another conveyor for further processing. Another sensor, positioned higher than the first, turns ON a different input to indicate that the product is too tall. The PC responds by turning on another pusher positioned before the pusher mentioned above to push the too-tall product into a rejection box.

Although this example involves only two inputs and two outputs, it is typical of the type of control operation that PCs can achieve. Actually even this example is much more complex than it may at first appear because of the timing that would be required, i.e., "How does the PC know when to activate each pusher?" Much more complicated operations, however, are also possible. The problem is how to get the desired control signals from available inputs at appropriate times.

To achieve proper control, the C1000H and C2000H use a form of PC logic called ladder-diagram programming. This manual is written to explain ladder-diagram programming and to prepare the reader to program and operate the C1000H and/or C2000H.

#### 1-2 Relay Circuits: The Roots of PC Logic

PCs historically originate in relay-based control systems. And although the integrated circuits and internal logic of the PC have taken the place of the discrete relays, timers, counters, and other such devices, actual PC operation proceeds as if those discrete devices were still in place. PC control, however, also provides computer capabilities and accuracy to achieve a great deal more flexibility and reliability than is possible with relays.

The symbols and other control concepts used to describe PC operation also come from relay-based control and form the basis of the ladder-diagram programming method. Most of the terms used to describe these symbols and concepts, however, have come in from computer terminology.

**Relay vs. PC Terminology** The terminology used throughout this manual is somewhat different from relay terminology, but the concepts are the same.

The following table shows the relationship between relay terms and the PC terms used for OMRON PCs.

| Relay term | PC equivalent             |

|------------|---------------------------|

| contact    | input or condition        |

| coil       | output or work bit        |

| NO relay   | normally open condition   |

| NC relay   | normally closed condition |

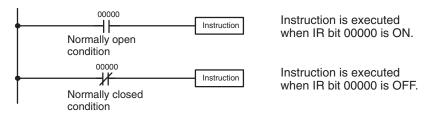

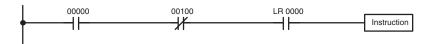

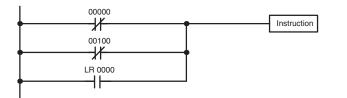

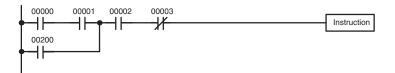

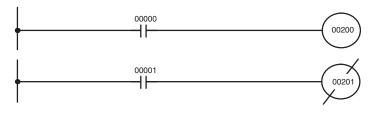

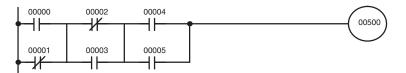

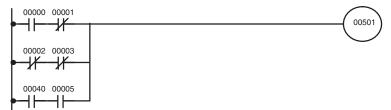

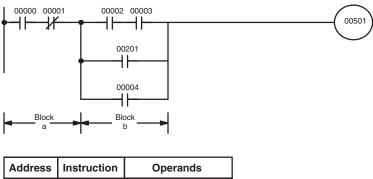

Actually there is not a total equivalence between these terms. The term condition is only used to describe ladder diagram programs in general and is specifically equivalent to one of certain set of basic instructions. The terms input and output are not used in programming per se, except in reference to I/O bits that are assigned to input and output signals coming into and leaving the PC. Normally open conditions and normally closed conditions are explained in *4-2 The Ladder Diagram*.

#### 1-3 PC Terminology

Although also provided in the *Glossary* at the back of this manual, the following terms are crucial to understanding PC operation and are thus explained here.

PC

Because the C1000H and C2000H are Rack PCs, there is no one product that is a C1000H or C2000H PC. That is why we talk about the configuration of the PC, because a PC is a configuration of smaller Units.

To have a functional PC, you would need to have a CPU Rack with at least one Unit mounted to it that provides I/O points. With a Duplex System, you would also need an CPU I/O Rack to mount the I/O Unit, because the Duplex CPU Rack does not provide slots for mounting other Units. When we refer to the PC, however, we are generally talking about the CPU and all of the Units directly controlled by it through the program. This does not include the I/O devices connected to PC inputs and outputs.

If you are not familiar with the terms used above to describe a PC, refer to *2-2 Hardware Considerations* for explanations.

Inputs and Outputs A device connected to the PC that sends a signal to the PC is called an input device; the signal it sends is called an input signal. A signal enters the PC through terminals or through pins on a connector on a Unit. The place where a signal enters the PC is called an input point. This input point is allocated a location in memory that reflects its status, i.e., either ON or OFF. This memory location is called an input bit. The CPU, in its normal processing cycle, monitors the status of all input points and turns ON or OFF corresponding input bits accordingly.

There are also **output bits** in memory that are allocated to **output points** on Units through which **output signals** are sent to **output devices**, i.e., an output bit is turned ON to send a signal to an output device through an output point. The CPU periodically turns output points ON or OFF according to the status of the output bits.

These terms are used when describing different aspects of PC operation. When programming, one is concerned with what information is held in memory, and so I/O bits are referred to. When talking about the Units that connect the PC to the controlled system and the places on these Units where signals enter and leave the PC, I/O points are referred to. When wiring these I/O points, the physical counterparts of the I/O points, either terminals or connector pins, are referred to. When talking about the signals that enter or leave the PC, one refers to input signals and output signals, or sometimes just inputs and outputs. It all depends on what aspect of PC operation is being talked about.

Controlled System and Control System The Control System includes the PC and all I/O devices it uses to control an external system. A sensor that provides information to achieve control is an input device that is clearly part of the Control System. The controlled system is the external system that is being controlled by the PC program through these I/O devices. I/O devices can sometimes be considered part of the controlled system, e.g., a motor used to drive a conveyor belt.

#### 1-4 OMRON Product Terminology

OMRON products are divided into several functional groups that have generic names. Appendix A Standard Models list products according to these groups. The term **Unit** is used to refer to all of the OMRON PC products. Although a Unit is any one of the building blocks that goes together to form a C1000H or C2000H PC, its meaning is generally, but not always, limited in context to refer to the Units that are mounted to a Rack. Most, but not all, of these products have names that end with the word Unit.

The largest group of OMRON products is the **I/O Units**. These include all of the Rack-mounting Units that provide non-dedicated input or output points for general use. I/O Units come with a variety of point connections and specifications.

**Special I/O Units** are dedicated Units that are designed to meet specific needs. These include Position Control Units, High-speed Counter Units, and Analog I/O Units. This group also includes some programmable Units, such as the ASCII Unit, which is programmed in BASIC.

**Link Units** are used to create Link Systems that link more than one PC or link a single PC to remote I/O points. Link Units include Remote I/O Units, PC Link Units, SYSMAC NET Link Units, and Host Link Units.

Other product groups include **Programming Devices**, **Peripheral Devices**, and **DIN Rail Products**.

#### 1-5 Overview of PC Operation

The following are the basic steps involved in programming and operating a C1000H or C2000H. Assuming you have already purchased one or more of these PCs, you must have a reasonable idea of the required information for steps one and two, which are discussed briefly below. This manual is written to explain steps three through six, eight, and nine. The relevant sections of this manual that provide more information are listed with each of these steps.

- *1, 2, 3...* 1. Determine what the controlled system must do, in what order, and at what times.

- 2. Determine what Racks and what Units will be required. Refer to the *C1000H/C2000H Installation Guide*. If a Link System is required, refer to the appropriate *System Manual*.

- 3. On paper, assign all input and output devices to I/O points on Units and determine which I/O bits will be allocated to each. If the PC includes Special I/O Units or Link Systems, refer to the individual *Operation Manuals* or *System Manuals* for details on I/O bit allocation. (*Section 3 Memory Areas*)

- 4. Using relay ladder symbols, write a program that represents the sequence of required operations and their inter-relationships. Be sure to also program appropriate responses for all possible emergency situations. (*Section 4 Writing and Inputting the Program, Section 5 Instruction Set, Section 6 Program Execution Timing*)

- 5. Input the program and all required operating parameters into the PC. (*Section 7 Program Input, Debugging, and Execution*)

- 6. Debug the program, first to eliminate any syntax errors, and then to find execution errors. (*Section 7 Program Input, Debugging, and Execution* and *Section 8 Troubleshooting*)

|                                        | <ol> <li>Wire the PC to the controlled system. This step can actually be started<br/>as soon as step 3 has been completed. Refer to the <i>C1000H/C2000H</i><br/><i>Installation Guide</i> and to <i>Operation Manuals</i> and <i>System Manuals</i> for<br/>details on individual Units.</li> <li>Test the program in an actual control situation and carry out fine tuning<br/>as required. (<i>Section 4 Writing and Inputting the Program, Section 7</i><br/><i>Program Debugging and Execution,</i> and <i>Section 8 Troubleshooting</i>)</li> <li>Record two copies of the finished program on masters and store them<br/>safely in different locations. (<i>Section 7 Program Debugging and Execu-<br/>tion</i>)</li> </ol> |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control System Design                  | Designing the Control System is the first step in automating any process. A PC can be programmed and operated only after the overall Control System is fully understood. Designing the Control System requires, first of all, a thorough understanding of the system that is to be controlled. The first step in designing a Control System is thus determining the requirements of the controlled system.                                                                                                                                                                                                                                                                                                                         |

| Input/Output Requirements              | The first thing that must be assessed is the number of input and output points that the controlled system will require. This is done by identifying each device that is to send an input signal to the PC or which is to receive an output signal from the PC. Keep in mind that the number of I/O points available depends on the configuration of the PC. Refer to <i>3-2 IR Area</i> for details on I/O capacity and the allocation of I/O bits to I/O points.                                                                                                                                                                                                                                                                  |

| Sequence, Timing, and<br>Relationships | Next, determine the sequence in which control operations are to occur and the relative timing of the operations. Identify the physical relationships be-<br>tween the I/O devices as well as the kinds of responses that should occur between them.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                        | For instance, a photoelectric switch might be functionally tied to a motor by<br>way of a counter within the PC. When the PC receives an input from a start<br>switch, it could start the motor. The PC could then stop the motor when the<br>counter has received a specified number of input signals from the photoelec-<br>tric switch.                                                                                                                                                                                                                                                                                                                                                                                         |

|                                        | Each of the related tasks must be similarly determined, from the beginning of the control operation to the end.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Unit Requirements                      | The actual Units that will be mounted or connected to PC Racks must be de-<br>termined according to the requirements of the I/O devices. Actual hardware<br>specifications, such as voltage and current levels, as well as functional con-<br>siderations, such as those that require Special I/O Units or Link Systems will<br>need to be considered. In many cases, Special I/O Units, Intelligent I/O Units,<br>or Link Systems can greatly reduce the programming burden. Details on<br>these Units and Link Systems are available in appropriate <i>Operation Manu-<br/>als</i> and <i>System Manuals</i> .                                                                                                                   |

|                                        | Once the entire Control System has been designed, the task of program-<br>ming, debugging, and operation as described in the remaining sections of<br>this manual can begin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### **1-6** Peripheral Devices

The following peripheral devices can be used in programming, either to input/ debug/monitor the PC program or to interface the PC to external devices to output the program or memory area data. Model numbers for all devices listed below are provided in *Appendix A Standard Models*. OMRON product

|                                 | names have been placed in bold when introduced in the following descrip-<br>tions.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programming Console             | A Programming Console is the simplest form of programming device for OM-<br>RON PCs. Although a <b>Programming Console Adapter</b> is sometimes re-<br>quired, all Programming Consoles are connected directly to the CPU without<br>requiring a separate interface. The Programming Console also functions as<br>an interface to transfer programs to a standard cassette tape recorder.                                                                                                                                                    |

|                                 | Various types of Programming Console are available, including both CPU-mounting and Hand-held models. Programming Console operations are described later in this manual.                                                                                                                                                                                                                                                                                                                                                                     |

| Graphic Programming<br>Console: | The GPC allows you to perform all the operations of the Programming Con-<br>sole as well as many additional ones. PC programs can be written on-screen<br>in ladder-diagram form as well as in mnemonic form. As the program is writ-<br>ten, it is displayed on a liquid crystal display, making confirmation and modifi-<br>cation quick and easy. Syntax checks may also be performed on the pro-<br>grams before they are downloaded to the PC. Many other functions are avail-<br>able, depending on the Memory Pack used with the GPC. |

|                                 | A Peripheral Interface Unit is required to interface the GPC to the PC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                 | The GPC also functions as an interface to copy programs directly to a stan-<br>dard cassette tape recorder. A <b>PROM Writer</b> , <b>Floppy Disk Interface Unit</b> , or<br><b>Printer Interface Unit</b> can be directly mounted to the GPC to output pro-<br>grams directly to an EPROM chip, floppy disk drive, or printing device, re-<br>spectively.                                                                                                                                                                                   |

| Ladder Support Software:<br>LSS | LSS is designed to run on IBM AT/XT compatibles to enable all of the opera-<br>tions available on the GPC. Using an Optical Host Link Unit also enables the<br>use of optical fiber cable to connect the FIT to the PC. Wired Host Link Units<br>are available when desired. (Although FIT does not have optical connectors,<br>conversion to optical fiber cable is possible by using <b>Converting Link</b><br><b>Adapters</b> .)                                                                                                          |

|                                 | A Host Link Unit is required to interface a computer running LSS to the PC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                 | The FIT is an OMRON computer with specially designed software that allows you to perform all of the operations that are available with the GPC or LSS. Programs can also be output directly to an EPROM chip, floppy disk drive, or printing device without any additional interface. The FIT has an EPROM writer and two 3.5" floppy disk drives built in.                                                                                                                                                                                  |

|                                 | A <b>Peripheral Interface Unit</b> or <b>Host Link Unit</b> is required to interface the FIT to the PC. Using an Optical Host Link Unit also enables the use of optical fiber cable to connect the FIT to the PC. Wired Host Link Units are available when desired. (Although FIT does not have optical connectors, conversion to optical fiber cable is possible by using <b>Converting Link Adapters</b> .)                                                                                                                                |

| PROM Writer                     | Other than its applications described above, the PROM Writer can be mounted to the PC's CPU to write programs to EPROM chips.                                                                                                                                                                                                                                                                                                                                                                                                                |

| Floppy Disk Interface Unit      | Other than its applications described above, the Floppy Disk Interface Unit can be mounted to the PC's CPU to interface a floppy disk drive and write programs onto floppy disks.                                                                                                                                                                                                                                                                                                                                                            |

| Printer Interface Unit          | Other than its applications described above, the Printer Interface Unit can be mounted to the PC's CPU to interface a printer or X-Y plotter to print out pro-<br>grams in either mnemonic or ladder-diagram form.                                                                                                                                                                                                                                                                                                                           |

#### 1-7 Available Manuals

The following table lists other manuals that may be required to program and/ or operate the C1000H and C2000H. *Operation Manuals* and/or *Operation Guides* are also provided with individual Units and are required for wiring and other specifications.

| Name                                       | Cat. No. | Contents                                                                                                                                                      |

|--------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1000H/C2000H Operation Manual             | W140     | Software specifications                                                                                                                                       |

| GPC Operation Manual                       | W84      | Programming procedures for the GPC (Graphics<br>Programming Console)                                                                                          |

| FIT Operation Manual                       | W150     | Programming procedures for using the FIT (Factory Intelligent Terminal                                                                                        |

| LSS Operation Manual                       | W237     | Programming procedures for using LSS (Ladder Support Software)                                                                                                |

| Data Access Console Operation Guide        | W173     | Data area monitoring and data modification procedures for the Data Access Console                                                                             |

| Printer Interface Unit Operation Guide     | W107     | Procedures for interfacing a PC to a printer                                                                                                                  |

| PROM Writer Operation Guide                | W155     | Procedures for writing programs to EPROM chips                                                                                                                |

| Floppy Disk Interface Unit Operation Guide | W119     | Procedures for interfacing a PC to a floppy disk drive                                                                                                        |

| Wired Remote I/O System Manual             | W120     | Information on building a Wired Remote I/O System to enable remote I/O capability                                                                             |

| Optical Remote I/O System Manual           | W136     | Information on building an Optical Remote I/O System to enable remote I/O capability                                                                          |

| PC Link System Manual                      | W135     | Information on building a PC Link System to automatically transfer data between PCs                                                                           |

| Host Link System Manual                    | W143     | Information on building a Host Link System to manage<br>PCs from a 'host' computer                                                                            |

| SYSMAC NET Link System Manual              | W114     | Information on building a SYSMAC NET Link System and<br>thus create an optical LAN integrating PCs with<br>computers and other peripheral devices             |

| SYSMAC LINK System Manual                  | W174     | Information on building a SYSMAC LINK System to<br>enable automatic data transfer, programming, and<br>programmed data transfer between the PCs in the System |

#### SECTION 2 Hardware Considerations

This section provides information on hardware aspects of the C1000H and C2000H that are relevant to programming and software operation. These include indicators on the CPU and Duplex Unit and basic PC configuration. This information is covered in detail in the *C1000H/C2000H Installation Guide*.

| 2-1 | Indicators       | 10 |

|-----|------------------|----|

| 2-2 | PC Configuration | 12 |

#### 2-1 Indicators

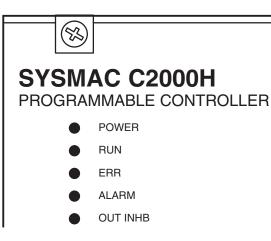

CPU and Duplex Unit indicators provide visual information on the general operation of the PC. Although not substitutes for proper error programming using the flags and other error indicators provided in the data areas of memory, these indicators provide ready confirmation of proper operation.

**CPU Indicators**

CPU indicators are shown below and are described in the following table. Indicators are the same for both C1000H and C2000H.

| Indicator | Function                                                                                                                                                                                                             |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER     | Lights when power is supplied to the CPU.                                                                                                                                                                            |

| RUN       | Lights when the CPU is operating normally.                                                                                                                                                                           |

| ERR       | Lights when an error is discovered in error diagnosis operations.<br>When this indicator lights, the RUN indicator will go off, CPU<br>operation will be stopped, and all outputs from the PC will be<br>turned OFF. |

| ALARM     | Lights when an error is discovered in error diagnosis operations.<br>PC operation will continue.                                                                                                                     |

| OUT INHB  | Lights when the Output OFF bit, SR bit 25215, is turned ON. All outputs from the PC will be turned OFF.                                                                                                              |

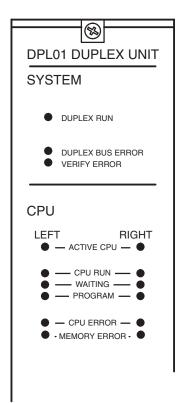

#### **Duplex Unit Indicators**

Duplex Unit indicators are shown and described below. Refer to the *C1000H/C2000H Installation Guide* for details. Duplex operation is only available on C2000H Units.

| Indicator           | Function                                                                                                                                                                                                                       |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DUPLEX RUN          | Lights when the Duplex Unit is operating normally.                                                                                                                                                                             |

| DUPLEX BUS<br>ERROR | Lights when an error has occurred in the Duplex Unit bus. The DUPLEX RUN indicator will go out and the active CPU will switch to simplex operation.                                                                            |

| VERIFY<br>ERROR     | Lights when the two CPUs do not contain the same program. The DUPLEX RUN indicator will go out and the active CPU will switch to simplex operation.                                                                            |

| ACTIVE CPU          | Indicate which CPU is active.                                                                                                                                                                                                  |

| CPU RUN             | Lights whenever the RUN indicators on the CPUs are lit.                                                                                                                                                                        |

| WAITING             | Lights at the beginning of duplex operation until the programs<br>have been verified (1 to 20 seconds). Will remain lit if program<br>execution does not start properly or if an error occurs in starting<br>duplex operation. |

| PROGRAM             | Lights when the PCs are in PROGRAM mode.                                                                                                                                                                                       |

| CPU ERROR           | Lights when CPU errors occur in the CPUs. CPU operation will stop and the CPU RUN indicator will go out.                                                                                                                       |

| MEMORY<br>ERROR     | Lights when memory errors occur in the CPUs. CPU operation will stop and the CPU RUN indicator will go out.                                                                                                                    |

## 2-2 PC Configuration

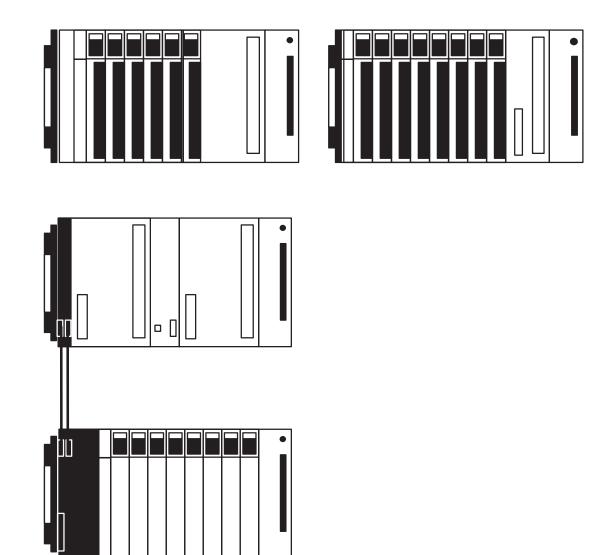

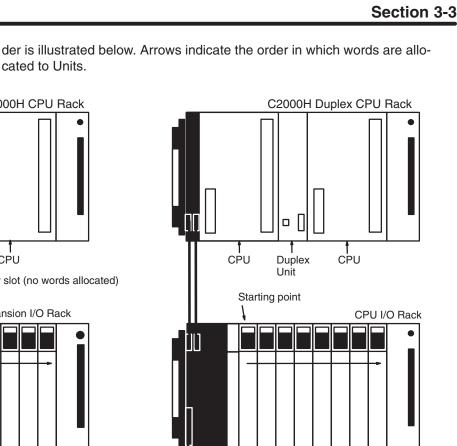

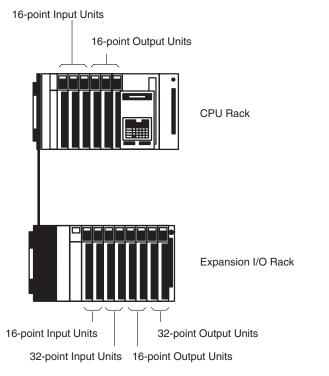

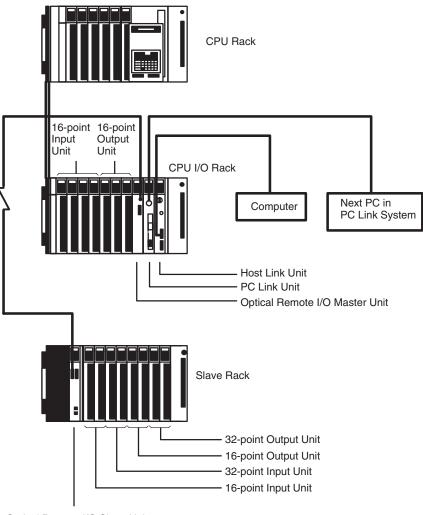

|                     | The basic PC configuration consists of either two or three types of Rack: a CPU Rack and Expansion I/O Racks for C2000H Simplex Systems and the C1000H, and a CPU Rack, a CPU I/O Rack, and Expansion I/O Racks for C2000H Duplex Systems. The Expansion I/O Racks are not a required part of the basic system. They are used to increase the number of I/O points. An illustration of these Racks is provided in <i>3-2 IR Area.</i> A fourth type of Rack, called a Slave Rack, can be used when the PC is provided with a Remote I/O System. |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU Racks           | A C2000H Simplex CPU Rack or C1000H CPU Rack consists of four components: (1) The CPU Backplane, to which the CPU, the Power Supply, and other Units are mounted. (2) The CPU, which executes the program and controls the PC. (3) Other Units, such as I/O Units, Special I/O Units, Link Units, and Intelligent I/O Units, which provide the physical I/O terminals corresponding to I/O points. (4) The Power Supply, which provides power to the CPU Rack.                                                                                  |

|                     | A C2000H Simplex or C1000H CPU Rack can be used alone or it can be<br>connected to other Racks to provide additional I/O points. The C1000H CPU<br>Rack provides five or eight slots to which these other Units can be mounted<br>depending on the backplane used; the C2000H Simplex CPU Rack provides<br>six slots.                                                                                                                                                                                                                           |

|                     | A C2000H Duplex CPU Rack Consists of a Duplex CPU Backplane, two<br>CPUs connected by a Duplex Unit, and a Power Supply. A Duplex CPU Rack<br>is completely filled by these Units and does not provide any slots for other<br>Units.                                                                                                                                                                                                                                                                                                            |

|                     | In a Duplex System, one of the two CPUs is active and the other is on<br>standby as long as both are operating normally. Both CPUs must contain the<br>same size and type of Memory Unit, and the same program. If the active<br>CPU fails to operate normally, the standby CPU takes control with simplex<br>operation until normal duplex operation can be restored. If an error occurs in<br>the standby CPU or in the Duplex Unit, the active CPU switches to simplex<br>operation. The Duplex Unit coordinates these processes.            |

| CPU I/O Racks       | To provide slots for other Units in a C2000H Duplex System, a CPU I/O Rack<br>is connected to the CPU Rack. The CPU I/O Rack is built on a I/O Back-<br>plane, which provides eight slots for other Units. In a Duplex System, one<br>CPU Rack and one CPU I/O Rack are used in a pair. The CPU has no<br>means of sending and receiving I/O signals without an I/O Rack. The I/O<br>Rack is always connected to a C2000H Duplex CPU via the connectors on<br>the Backplanes, allowing communication between the two Racks.                     |

| Expansion I/O Racks | An Expansion I/O Rack can be thought of as an extension of the PC because<br>it provides additional slots to which other Units can be mounted. It is built<br>onto an Expansion I/O Backplane to which a Power Supply and up to eight<br>other Units are mounted.                                                                                                                                                                                                                                                                               |

|                     | An I/O Interface Unit is also mounted to any Expansion I/O Rack to interface<br>the Rack to the CPU Rack. Also, an I/O Control Unit must be mounted to any<br>C1000H or C2000H Simplex CPU Rack to which one or more Expansion I/O<br>Racks are mounted. In a C2000H Duplex System the I/O Control Unit is<br>mounted to the CPU I/O Rack.                                                                                                                                                                                                      |

|                     | An Expansion I/O Rack is always connected to the CPU via the connectors on the Backplanes, allowing communication between the two Racks. In a                                                                                                                                                                                                                                                                                                                                                                                                   |

C1000H System, or in C2000H Simplex or Duplex Systems, up to seven Expansion I/O Racks can be connected in series to the CPU Rack or, in a C2000H Duplex System, to the CPU I/O Rack.

Unit Mounting Position Only I/O Units and Special I/O Units can be mounted to Slave Racks. All I/O Units, Special I/O Units, Remote I/O Master Units, and I/O Link Units can be mounted to any slot on all other Racks. All other Units, including Interrupt Input Units, File Memory Units, and all other Link Units must be mounted only to certain slots on specific Racks. All Units occupy only one slot except for the PID Unit and some Position Control Units.

All Units that do not require specific slots can be mounted in any order. Units that do require specific slots can be mounted in any order within the required slots.

Refer to the *C1000H/C2000H Installation Guide* for details about which slots can be used for which Units and other details about PC configuration. The way in which I/O points on Units are allocated in memory is described in *3-2 IR Area*.

### **SECTION 3 Memory Areas**

Various types of data are required to achieve effective and correct control. To facilitate managing this data, the PC is provided with various **memory areas** for data, each of which performs a different function. The areas generally accessible by the user for use in programming are classified as **data areas**..

The other memory areas include the Program Memory, where the user's program is actually stored, as well as Trace Memory and File Memory. This section describes these areas individually and provides information that will be necessary to use them. As a matter of convention, the TR area is described in this section, even though it is not strictly a memory area.

| 3-1  | Introduction                   |                                                 |    |  |  |  |  |  |

|------|--------------------------------|-------------------------------------------------|----|--|--|--|--|--|

| 3-2  | Data Ar                        | rea Structure                                   | 16 |  |  |  |  |  |

| 3-3  | IR (Inte                       | ernal Relay)Area                                | 18 |  |  |  |  |  |

| 3-4  | SR (Spe                        | ecial Relay) Area                               | 23 |  |  |  |  |  |

|      | 3-4-1                          | Link System Flags and Control Bits              | 24 |  |  |  |  |  |

|      | 3-4-2                          | Data Retention Control Bit                      | 28 |  |  |  |  |  |

|      | 3-4-3                          | Output OFF Bit                                  | 29 |  |  |  |  |  |

|      | 3-4-4                          | FAL (Failure Alarm) Area                        | 29 |  |  |  |  |  |

|      | 3-4-5                          | Low Battery Flag                                | 29 |  |  |  |  |  |

|      | 3-4-6                          | Cycle Time Error Flag                           | 29 |  |  |  |  |  |

|      | 3-4-7                          | I/O Verification Error Flag                     | 29 |  |  |  |  |  |

|      | 3-4-8                          | First Cycle Flag                                | 29 |  |  |  |  |  |

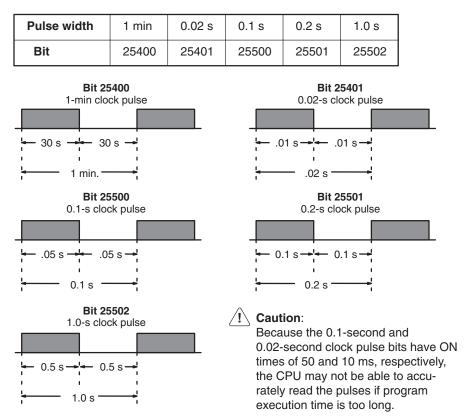

|      | 3-4-9                          | Clock Pulse Bits                                | 29 |  |  |  |  |  |

|      | 3-4-10                         | Step Flag                                       | 30 |  |  |  |  |  |

|      | 3-4-11                         | Duplex System Flags                             | 30 |  |  |  |  |  |

|      | 3-4-12                         | Instruction Execution Error Flag, ER            | 30 |  |  |  |  |  |

|      | 3-4-13                         | Arithmetic Flags                                | 31 |  |  |  |  |  |

| 3-5  | AR (Au                         | ixiliary Relay) Area                            | 31 |  |  |  |  |  |

|      | 3-5-1 S                        | YSMAC LINK System Data Link Settings            | 33 |  |  |  |  |  |

|      | 3-5-2 A                        | ctive Node Flags                                | 33 |  |  |  |  |  |

|      | 3-5-3                          | SYSMAC LINK/SYSMAC NET Link System Service Time | 34 |  |  |  |  |  |

|      | 3-5-4                          | Tracing Flags and Control Bits                  | 34 |  |  |  |  |  |

|      | 3-5-5                          | File Memory Flags and Control Bits              | 34 |  |  |  |  |  |

|      | 3-5-6                          | On-line Removal Bits                            | 35 |  |  |  |  |  |

|      | 3-5-7                          | Power-off Counter                               | 35 |  |  |  |  |  |

|      | 3-5-8                          | Network Parameter Flags                         | 36 |  |  |  |  |  |

|      | 3-5-9                          | Link Unit Mounted Flags                         | 36 |  |  |  |  |  |

|      | 3-5-10                         | CPU-mounting Device Flag                        | 36 |  |  |  |  |  |

|      | 3-5-11                         | FALS-generating Address                         | 36 |  |  |  |  |  |

|      | 3-5-12                         | Cycle Time Indicators                           | 36 |  |  |  |  |  |

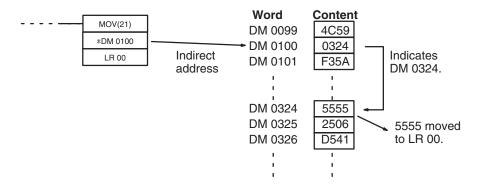

| 3-6  | DM (Da                         | ata Memory) Area                                | 36 |  |  |  |  |  |

| 3-7  | HR (Ho                         | olding Relay) Area                              | 37 |  |  |  |  |  |

| 3-8  | TC (Tin                        | ner/Counter) Area                               | 37 |  |  |  |  |  |

| 3-9  | LR (Lin                        | nk Relay) Area                                  | 38 |  |  |  |  |  |

| 3-10 | Program                        | n Memory                                        | 39 |  |  |  |  |  |

| 3-11 | File Me                        | mory                                            | 39 |  |  |  |  |  |

| 3-12 | Trace M                        | Iemory                                          | 39 |  |  |  |  |  |

| 3-13 | 3 TR (Temporary Relay) Area 39 |                                                 |    |  |  |  |  |  |

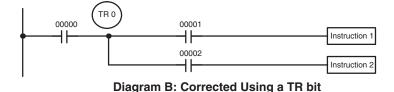

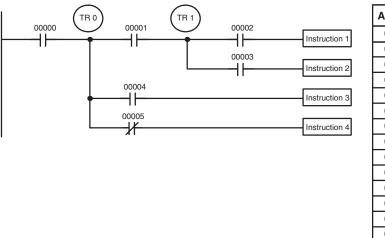

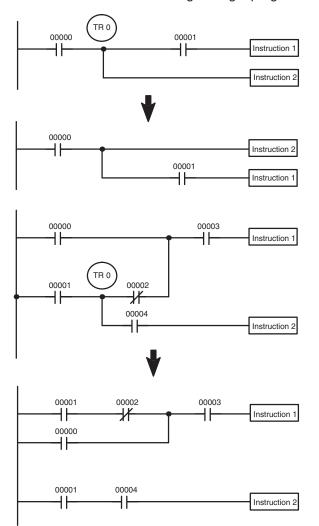

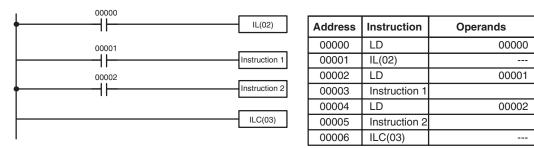

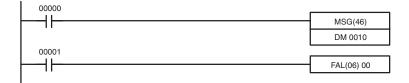

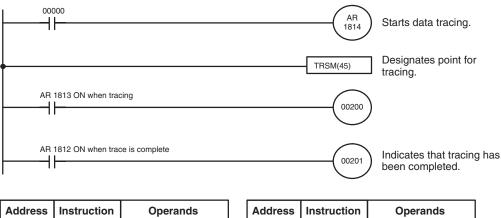

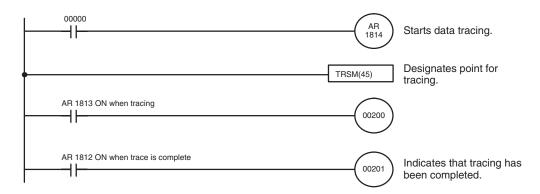

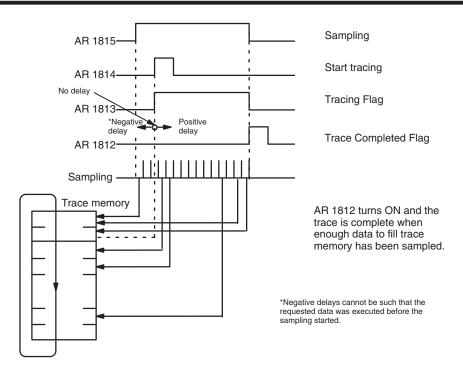

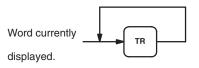

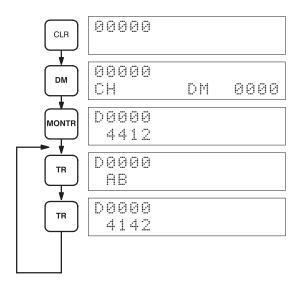

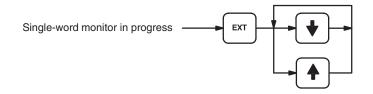

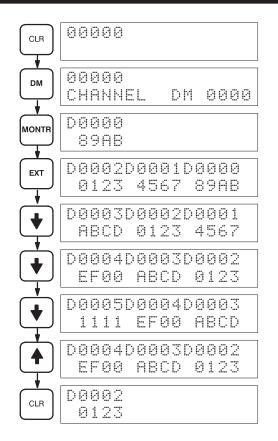

#### 3-1 Introduction